# A Novel Passive Regenerative Snubber for the Phase-Shifted Full-Bridge Converter: Analysis, Design and Experimental Verification

A THESIS

SUBMITTED FOR THE DEGREE OF

Master of Technology (Research)

THE FACULTY OF ENGINEERING

$\begin{array}{c} \text{by} \\ \textbf{Shubham Rawat} \end{array}$

DEPARTMENT OF ELECTRICAL ENGINEERING INDIAN INSTITUTE OF SCIENCE BANGALORE 560 012

September 2022

# Dedication

This thesis is dedicated to my grandparents, parents and brother for their endless love and encouragement to follow my dreams.

# Acknowledgements

Firstly, I want to express my sincere gratitude to my advisor, Dr. Kaushik Basu, for being a great supervisor and mentor. His constant encouragement and advice has helped me to think independently and explore new ideas. He has always strived to provide us with the best working environment and state-of-the-art laboratory facilities. I want to express my appreciation for his excellent lectures on Embedded Systems Design for Power Electronics Applications and Advanced Power Electronics, shaping my understanding of various concepts of power electronics. His constant support and motivation to work hard has driven me during difficult times in this journey. I would always try to implement the technical and non-technical things I have learnt from him.

I express my profound gratitude to Dr. G Narayanan for his vivid way of teaching the Power Electronics and Pulse Width Modulated Converters and Applications courses. I sincerely thank Dr. Vinod John for his Switched Mode Power Conversion course. Their lectures on fundamental power-electronic courses have helped me multifold in my research work. I thank all the professors in IISc who have taught me different subjects and helped improve my understanding of various concepts.

I would also like to thank our EE office staff, Mr Kini, Mrs Amala, and Mr Rudresh, for their administrative work. I thank Mr Erwine Paul for his help regarding any projector-related issues faced during my presentation in MMCR.

I earnestly acknowledge MHRD, Govt. of India, for the financial support during this period and RBCCPS, IISc, for the research grant for this project.

I convey my thanks to my seniors, Dr. Anirban Pal, Dr. Shamibrota Roy Kishore, Sayan Paul, Dibakar Das, Manish Mandal, Kapil Upamanyu, Roja Peri, and Harisyam, for their encouragement and valuable input on different aspects of power electronics. Shamibrota Da deserves special thanks for being my second advisor cum friend in this research journey. I have been fortunate to share my lab with Sayan Da, Harisyam, Shamik, Shashank, Jagdeesh, Ankita, and Surjakanta. I am grateful to my friends and PEG labmates Manish Tathode, Anuj Kumar, Vihan Sahu, Anand Kumar, Shamik, Shashank, and Ankita for their help and insightful suggestions. I would also like to thank my juniors, Ankit, Rishil, Mayur, and Sairakshith.

I treasure the wonderful moments I shared with my friends Aksha, Rajat, Ashu, Pranay, Anchal, Gaurav, Anuj, Nitish, Jwala, Triloki, Anand Bhai, Ankit, and Pranjal during my stay at IISc.

Lastly, I thank my grandparents, parents, and Aksha for their constant love and support throughout this journey.

# Abstract

The development of Wide Bandgap (WBG) devices has enabled power electronic converters to operate at much higher frequencies, voltages and high power. Working at a higher switching frequency minimises the size of magnetics but results in significant switching losses and electromagnetic interference (EMI) noise. Thus, it necessitates the use of soft-switching techniques to reduce these losses. Phase-Shifted Full-Bridge (PSFB) Converter is the most widely used soft-switching topology in the high-voltage and high-power, unidirectional, DC-DC conversion. The phase shift PWM control utilises the converter parasitics to achieve zero voltage switching (ZVS) turn ON. The gating technique allows the magnetic energy stored in the leakage inductance of the isolation transformer to charge and discharge the output capacitances of the inverter leg. However, the converter suffers from severe voltage overshoots across the rectifier bridge during the zero to the active state transition. The resonant circuit formed between the transformer leakage inductance and the parasitic diode capacitance of the rectifier is responsible for the high-voltage ringing.

Many passive and active snubbers are presented in the literature to mitigate the highvoltage overshoots across the diode bridge. While passive snubbers are relatively simple to implement than active snubbers, they are lossy. On the other hand, the active snubbers require additional gate driver circuitry and complex control.

The first part of the thesis proposes a novel passive regenerative snubber to overcome the mentioned drawbacks of the existing snubbers. The proposed snubber is ideally lossless with no control complexity. The work covers a detailed analysis of the PSFB operation with the proposed snubber while obtaining closed-form expressions for the converter state variables at the end of each topological stage. The study considers all the major converter parasitics, such as transformer leakage and magnetising inductances, and parasitic capacitances of the converter. Given the new snubber, the thesis also lays out a step-by-step PSFB design procedure utilising the analysis carried out in the first part of the work. The design aimed to develop a 100 kHz PSFB for an input voltage of 360-440 V in the output power range of 0.5-1.5 kW at a fixed output voltage of 48 V. The design approach focuses on the two design objectives - All inverter switches must achieve ZVS turn ON and the desired converter gain for all possible operating conditions.

A hardware prototype is built and tested. The experimental results validate the effectiveness of the snubber in reducing the voltage overshoot. Further, the analysis and design accuracy is verified using the measured state variables. The work, at last, presents the overall converter efficiency and the loss distribution among the converter components.

# Contents

| 1 | Intr | roduction 1                                                                   |

|---|------|-------------------------------------------------------------------------------|

|   | 1.1  | Background and Motivation                                                     |

|   | 1.2  | Isolated Unidirectional DC-DC Converters                                      |

|   | 1.3  | Phase-Shifted Full-Bridge                                                     |

|   | 1.4  | The Problem of Secondary Voltage Overshoots                                   |

|   | 1.5  | Existing Snubber Solutions                                                    |

|   | 1.6  | Contribution of the Thesis                                                    |

|   |      | 1.6.1 The Proposed Snubber                                                    |

|   |      | 1.6.2 PSFB Design                                                             |

|   | 1.7  | Organisation of the Thesis                                                    |

| 2 | Pha  | se-Shifted Full-Bridge Analysis 10                                            |

|   | 2.1  | Introduction                                                                  |

|   | 2.2  | Operational Analysis                                                          |

|   |      | 2.2.1 Mode 1 (Lagging Leg Switching)                                          |

|   |      | 2.2.2 Mode 2 (Current Commutation - I)                                        |

|   |      | 2.2.3 Mode 3 (Current Commutation - II)                                       |

|   |      | 2.2.4 Mode 4 (Secondary Voltage Rise)                                         |

|   |      | 2.2.5 Mode 5 (Active State)                                                   |

|   |      | 2.2.6 Mode 6 (Leading Leg Switching)                                          |

|   |      | 2.2.7 Mode 7 (Secondary Voltage Fall)                                         |

|   |      | 2.2.8 Mode 8 (Zero State)                                                     |

|   | 2.3  | Average Output Voltage                                                        |

|   | 2.4  | Snubber Non-Idealities                                                        |

|   |      | 2.4.1 Effects of Snubber Transformer Leakage Inductance $L_a$ 27              |

|   |      | 2.4.2 Effects of Snubber Bridge Capacitance $C_a$                             |

|   | 2.5  | Deviations from the Analysis                                                  |

|   |      | 2.5.1 Sub-mode 5-A (Snubber Current Fall)                                     |

|   |      | 2.5.2 Sub-mode 5-B                                                            |

|   |      | 2.5.3 Effects on the Converter Operation                                      |

|   | 2.6  | Summary                                                                       |

| 3 | Pha  | se-Shifted Full-Bridge Design 33                                              |

|   | 3.1  | Introduction                                                                  |

|   | 3.2  | PSFB Design with the Proposed Snubber                                         |

|   | 3.3  | Step 1: Selection of Devices and Extraction of Capacitances                   |

|   |      | 3.3.1 Inverter Bridge Devices                                                 |

|   |      | 3.3.2 Secondary Bridge Diodes                                                 |

|   |      | 3.3.3 Snubber Bridge Diodes                                                   |

|   |      | 3.3.4 Extraction of Capacitances                                              |

|   | 3.4  | Step 2: Determine Transformer Turns Ratio $n$ and Leakage Inductance $L$ . 42 |

|   | 3.5  | Step 3: Dead-time selection                                                   |

|   | 3.6                                           | Step 4: Low Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   |                                               | 3.6.1 Filter Inductance $(L_f)$                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|   | 0.7                                           | 3.6.2 Filter Capacitance $(C_f)$                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|   | 3.7                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Ö                               |

| 4 | Har                                           | rdware Design 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|   | 4.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                               |

|   | 4.2                                           | Transformer Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

|   |                                               | 4.2.1 Core Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|   |                                               | 4.2.2 Primary and Secondary Turns                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|   |                                               | 4.2.3 Litz Wire Design                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |

|   |                                               | 4.2.4 Transformer Winding Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|   |                                               | 4.2.5 Analytical calculation of Leakage Inductance 5                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|   | 4.3                                           | Heat Sink Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5                               |

|   | 4.4                                           | Gate Driver Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                               |

|   | 4.5                                           | Output Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

|   | 4.6                                           | Other Converter Components                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                               |

|   | 4.7                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D                               |

| 5 | Exp                                           | perimental Verification 63                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                               |

|   | 5.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                               |

|   | 5.2                                           | Parameters Estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                               |

|   |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |

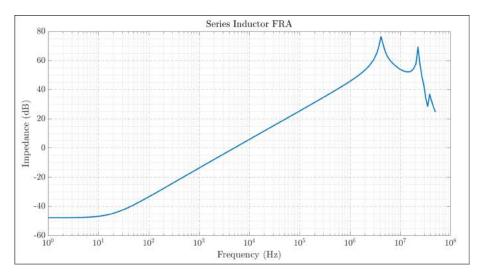

|   |                                               | 5.2.1 Parameter Estimation Using FRA 62                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                               |

|   |                                               | 5.2.1 Parameter Estimation Using FRA                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

|   | 5.3                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                               |

|   | 5.3<br>5.4                                    | 5.2.2 Parameter Estimation Using WE 67 Verification of the Snubber Operation                                                                                                                                                                                                                                                                                                                                                                                                      | 7<br>9                          |

|   |                                               | 5.2.2 Parameter Estimation Using WE 67 Verification of the Snubber Operation                                                                                                                                                                                                                                                                                                                                                                                                      | 7<br>9<br>2                     |

|   |                                               | 5.2.2 Parameter Estimation Using WE                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7<br>9<br>2                     |

|   |                                               | 5.2.2 Parameter Estimation Using WE67Verification of the Snubber Operation68PSFB Design Validation755.4.1 Objective I: The Converter Gain Verification75                                                                                                                                                                                                                                                                                                                          | 7<br>9<br>2<br>2<br>0           |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE67Verification of the Snubber Operation68PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification725.4.2 Objective II: Inverter Switches ZVS Turn-ON86                                                                                                                                                                                                                                                                       | 7<br>9<br>2<br>0<br>3           |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE67Verification of the Snubber Operation68PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification725.4.2 Objective II: Inverter Switches ZVS Turn-ON86Converter Efficiency and Loss Budgeting85                                                                                                                                                                                                                              | 7<br>9<br>2<br>0<br>3           |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE67Verification of the Snubber Operation68PSFB Design Validation735.4.1 Objective I: The Converter Gain Verification735.4.2 Objective II: Inverter Switches ZVS Turn-ON86Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses83                                                                                                                                                                                                | 7<br>9<br>2<br>0<br>3<br>3      |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE66Verification of the Snubber Operation69PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification735.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses835.5.2 Series Inductor Losses835.5.3 Main Transformer Losses84                                                                                                                                   | 7<br>9<br>2<br>0<br>3<br>3<br>4 |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE67Verification of the Snubber Operation68PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification735.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses835.5.2 Series Inductor Losses835.5.3 Main Transformer Losses84                                                                                                                                   | 792033346                       |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE66Verification of the Snubber Operation69PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification725.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses835.5.2 Series Inductor Losses835.5.3 Main Transformer Losses845.5.4 Secondary Diode Bridge Losses86                                                                                              | 7920334666                      |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE66Verification of the Snubber Operation69PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification725.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses835.5.2 Series Inductor Losses835.5.3 Main Transformer Losses845.5.4 Secondary Diode Bridge Losses865.5.5 Output Choke Losses86                                                                   | 79203334667                     |

|   | 5.4                                           | 5.2.2 Parameter Estimation Using WE66Verification of the Snubber Operation69PSFB Design Validation755.4.1 Objective I: The Converter Gain Verification755.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting855.5.1 Inverter bridge Losses855.5.2 Series Inductor Losses855.5.3 Main Transformer Losses865.5.4 Secondary Diode Bridge Losses865.5.5 Output Choke Losses865.5.6 Snubber Losses87                                             | 792033346679                    |

| 6 | <ul><li>5.4</li><li>5.5</li><li>5.6</li></ul> | 5.2.2 Parameter Estimation Using WE66Verification of the Snubber Operation69PSFB Design Validation725.4.1 Objective I: The Converter Gain Verification725.4.2 Objective II: Inverter Switches ZVS Turn-ON80Converter Efficiency and Loss Budgeting835.5.1 Inverter bridge Losses835.5.2 Series Inductor Losses835.5.3 Main Transformer Losses845.5.4 Secondary Diode Bridge Losses865.5.5 Output Choke Losses865.5.6 Snubber Losses875.5.7 Total Losses Distribution89            | 7920333466791                   |

| 6 | <ul><li>5.4</li><li>5.5</li><li>5.6</li></ul> | 5.2.2 Parameter Estimation Using WE Verification of the Snubber Operation  PSFB Design Validation  5.4.1 Objective I: The Converter Gain Verification  5.4.2 Objective II: Inverter Switches ZVS Turn-ON  Converter Efficiency and Loss Budgeting  5.5.1 Inverter bridge Losses  5.5.2 Series Inductor Losses  5.5.3 Main Transformer Losses  5.5.4 Secondary Diode Bridge Losses  5.5.5 Output Choke Losses  5.5.6 Snubber Losses  5.5.7 Total Losses Distribution  Summary  9.5 | 7920333466791                   |

# List of Tables

| 3.1<br>3.2 | Converter Specifications                                                                                         | $\frac{33}{37}$ |

|------------|------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.3        | Power dissipation table of different 200 V Si Schottky diodes                                                    | 38              |

| 3.4        | Paramters used to obtain the four plots using two extreme operating conditions.                                  | 43              |

| 3.5        | External Parasitic capacitance added to datasheet extracted capacitances, for the four plots                     | 43              |

| 4.1        | Core selection parameters of the transformers                                                                    | 49              |

| 4.2        | Primary and secondary turns of the two transformers                                                              | 50              |

| 4.3        | Litz wire structure of the four windings                                                                         | 52              |

| 4.4        | Winding data for the two transformers                                                                            | 53              |

| 4.5        | Thermal Components for the two bridges                                                                           | 55              |

| 4.6        | Other major converter components                                                                                 | 59              |

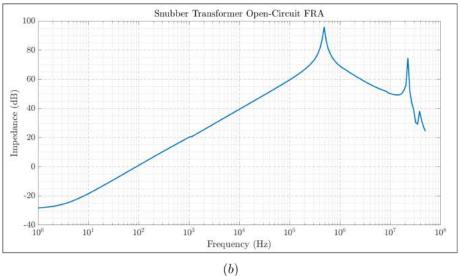

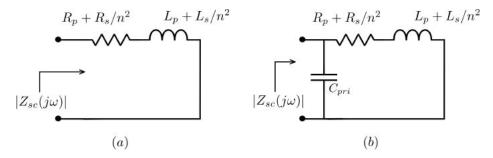

| 5.1        | Transformer parameters obtained from open-circuit test                                                           | 64              |

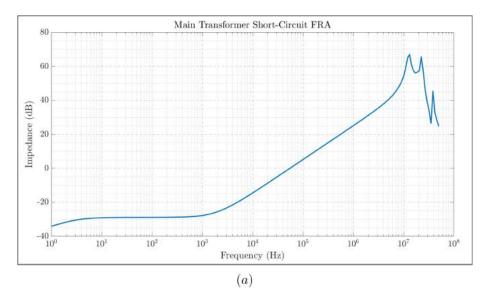

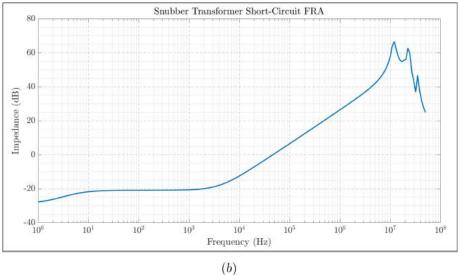

| 5.2        | Transformer parameters obtained from short-circuit test                                                          | 66              |

| 5.3        | Comparison of parameters estimated using FRA and WE to chosen design values                                      | 70              |

| 5.4        | Secondary Voltage overshoot comparison                                                                           | 71              |

| 5.5        | PSFB measured parameters                                                                                         | 72              |

| 5.6        | Analytical v/s Experimental mode interval comparison for Condition I                                             |                 |

|            | $(V_{dc} = 360 \text{V},  P_o = 1.5 \text{kW})$ and Condition II $(V_{dc} = 440 \text{V},  P_o = 0.5 \text{kW})$ | 72              |

| 5.7        | Analytical v/s experimental mode interval comparison for converter oper-                                         |                 |

|            | ating at $V_{dc} = 400 \text{ V}$ and $P_o \in [0.5 \text{ kW} - 1.5 \text{ kW}]$                                | 80              |

| 5.8        | Experimental and Analytical dead time comparison                                                                 | 80              |

| 5.9        | Primary bridge conduction losses                                                                                 | 84              |

| 5.10       | Series inductor conduction losses for primary currents at different power                                        |                 |

|            | levels.                                                                                                          | 84              |

| 5.11       | Main Transformer conduction losses for primary currents at different power                                       |                 |

|            | levels.                                                                                                          | 85              |

|            | Total power loss in the main transformer                                                                         | 86              |

|            | Conduction losses in the rectifier Bridge                                                                        | 86              |

| 5.14       | Filter choke conduction losses                                                                                   | 87              |

|            | Total loss contribution of the output choke                                                                      | 87              |

| 5.16       | Snubber Transformer conduction losses for snubber currents at different                                          |                 |

|            | power levels                                                                                                     | 88              |

| 5.17       | Snubber diode bridge conduction losses                                                                           | 88              |

| 5 18       | Total loss contribution of the snubber circuit                                                                   | 89              |

# List of Figures

| 1.1<br>1.2 | Phase-Shifted Full-Bridge Converter                                                                                                    | 2 3 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.3        | (a) Rectifier bridge during active mode. (b) Rectifier voltage overshoot                                                               | 3   |

| 1.5        | waveforms                                                                                                                              | 4   |

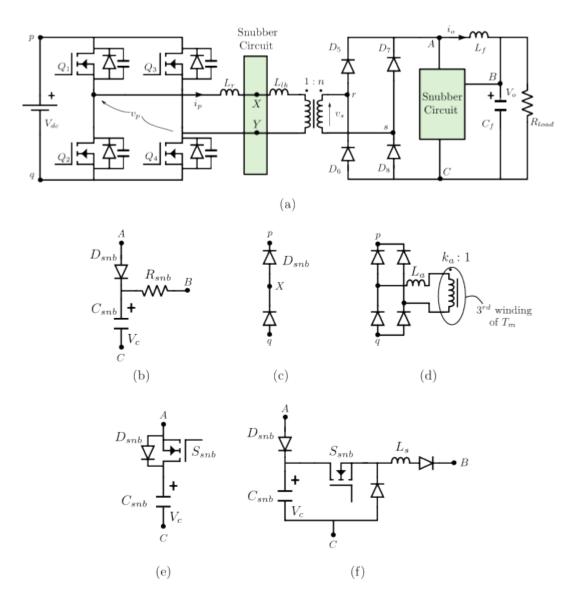

| 1.4        | Classification of snubbers for Phase-Shifted Full-Bridge                                                                               | 5   |

| 1.4        | PSFB converter with some popular snubber topologies. (a) Highlighted snubber positions. (b) RCD (c) Diode-Clamped Snubber (d) Winding- | J   |

|            | Clamped (e) Switch-Diode-Clamped (f) Auxiliary Buck Converter                                                                          | 6   |

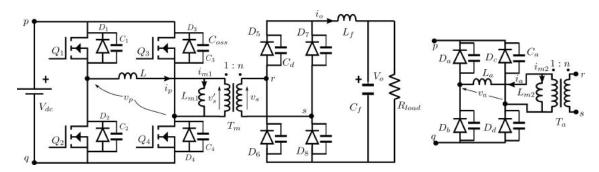

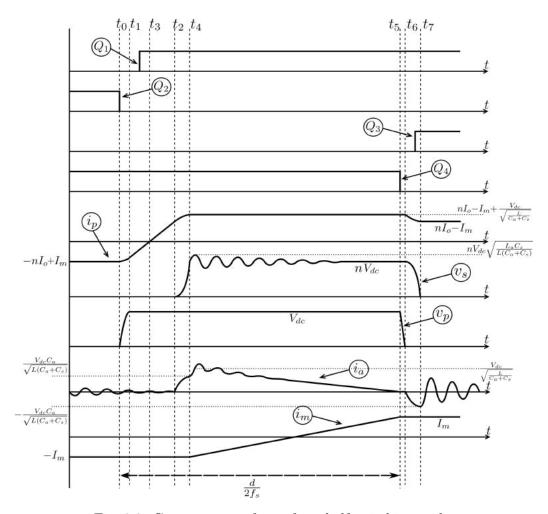

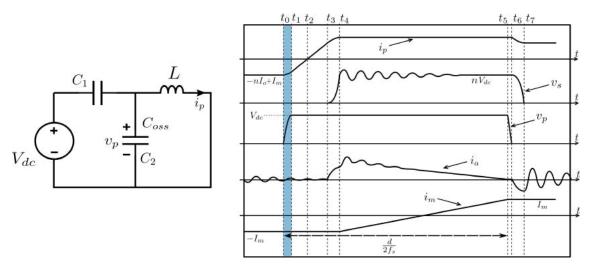

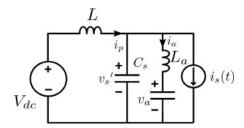

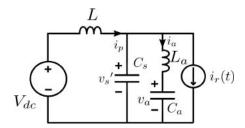

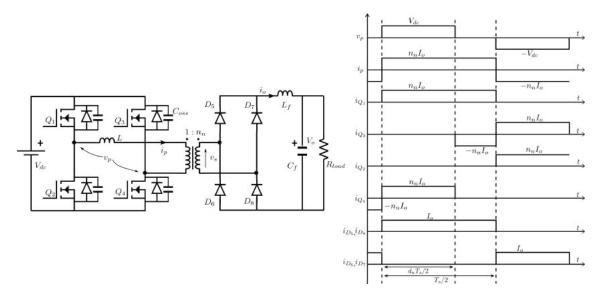

| 2.1        | PSFB converter with the proposed snubber                                                                                               | 10  |

| 2.2        | Converter waveforms for a half-switching cycle                                                                                         | 11  |

| 2.3        | Equivalent circuit for Mode 1                                                                                                          | 12  |

| 2.4        | Equivalent circuit for Mode 2                                                                                                          | 14  |

| 2.5        | Equivalent circuit for Mode 3                                                                                                          | 15  |

| 2.6        | Equivalent circuit for mode 4                                                                                                          | 16  |

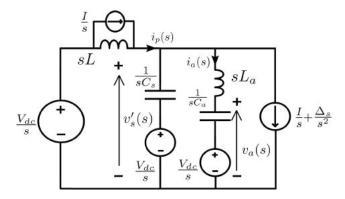

| 2.7        | Laplace transformed equivalent circuit for mode 4                                                                                      | 16  |

| 2.8        | Equivalent circuit for Mode 5                                                                                                          | 18  |

| 2.9        | Laplace transformed equivalent circuit for Mode 5                                                                                      | 19  |

| 2.10       | Equivalent circuit for Mode 6                                                                                                          | 21  |

|            | Equivalent Laplace transformation circuit for Mode 6                                                                                   | 21  |

|            | Equivalent circuit for Mode 7                                                                                                          | 23  |

|            | Laplace transformation equivalent circuit for mode 7                                                                                   | 24  |

|            | Equivalent circuit for Mode 8                                                                                                          | 25  |

| 2.15       | (a) Converter state variables considering the output current ripple and finite                                                         |     |

|            | magnetising inductance. (b) Transformation of the filter and magnetising                                                               |     |

|            | inductance to a ramping current sink.                                                                                                  | 28  |

|            | Sub-mode 5-A equivalent circuit.                                                                                                       | 29  |

|            | Sub-mode 5-B equivalent circuit                                                                                                        | 30  |

| 2.18       | Laplace transform equivalent circuit                                                                                                   | 30  |

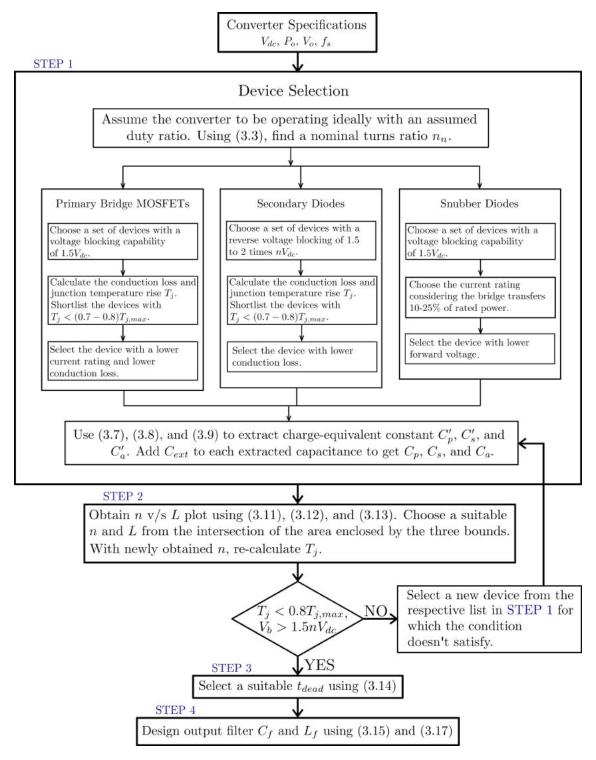

| 3.1        | PSFB Design Flow                                                                                                                       | 35  |

| 3.2        | Circuit diagram and associated waveforms of a PSFB converter without a                                                                 | 00  |

| J          | snubber. It is assumed that the output current is constant at $I_0$ . The duty                                                         |     |

|            | loss due to leakage inductance $L$ is neglected                                                                                        | 36  |

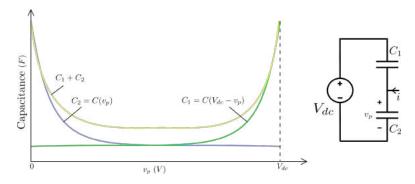

| 3.3        | The charging-discharging behaviour of the high and low side MOSFETs                                                                    | 40  |

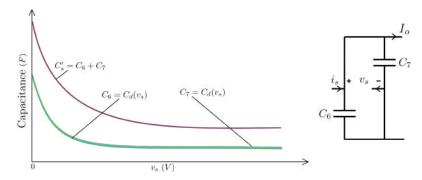

| 3.4        | Junction Capacitance vs reverse voltage characteristics of the secondary                                                               | 10  |

| J. I       | diode bridge                                                                                                                           | 40  |

| 3.5        | Simultaneous charging and discharging of snubber bridge capacitances                                                                   | 41  |

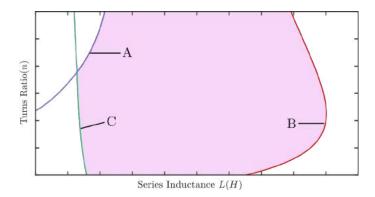

| 3.6        | $n \text{ v/s } L$ plot with the three constraints for a given $V_{dc}$ and $I_o$ , i.e. at a                                          | 11  |

|            | single operating point.                                                                                                                | 42  |

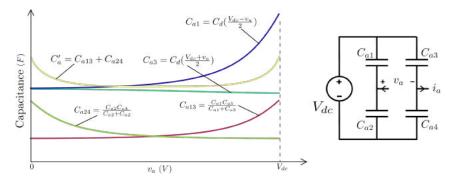

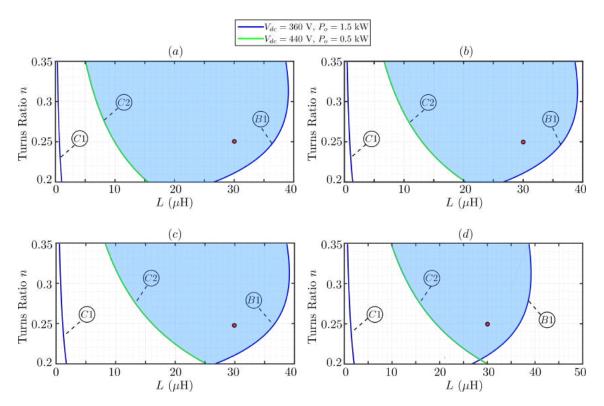

| 3.7  | $n \text{ v/s } L$ plots for the two extreme operating conditions. The four plots are for different external parasitic capacitances (a) $C_{ext} = 0 \text{ pF}$ , (b) $C_{ext} = 100 \text{ pF}$ , (c) $C_{ext} = 200 \text{ pF}$ , (d) $C_{ext} = 300 \text{ pF}$ | 44  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

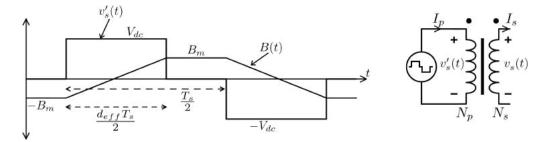

| 4.1  | Transformer's voltage and flux density waveforms                                                                                                                                                                                                                    | 48  |

| 4.2  | Approximate current waveform flowing through the main transformer                                                                                                                                                                                                   | 51  |

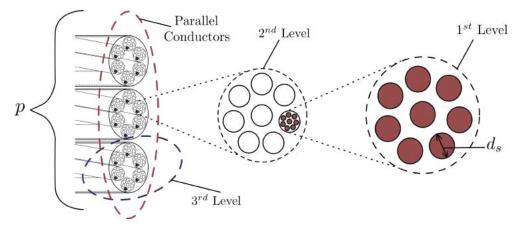

| 4.3  | General multi-level bundling structure of a litz wire                                                                                                                                                                                                               | 51  |

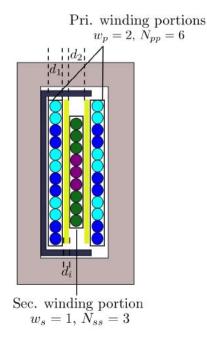

| 4.4  | Winding layout of the two transformers                                                                                                                                                                                                                              | 53  |

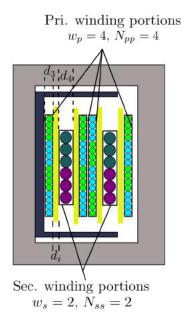

| 4.5  | MMF diagrams of the two transformer windings. The MMF diagrams are symmetrical and have been derived using the winding layout in Fig 4.4                                                                                                                            | 54  |

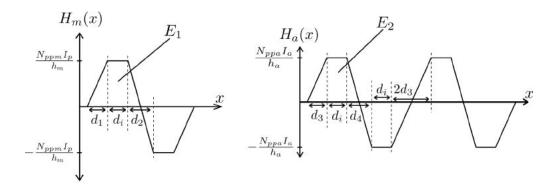

| 4.6  | Steady state thermal model of the bridges                                                                                                                                                                                                                           | 55  |

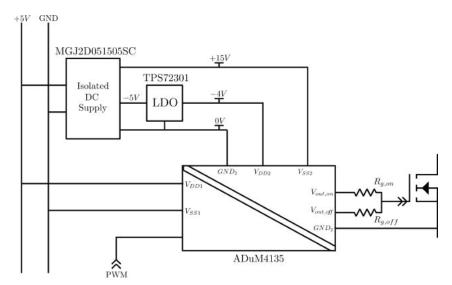

| 4.7  | Gate driver circuit                                                                                                                                                                                                                                                 | 56  |

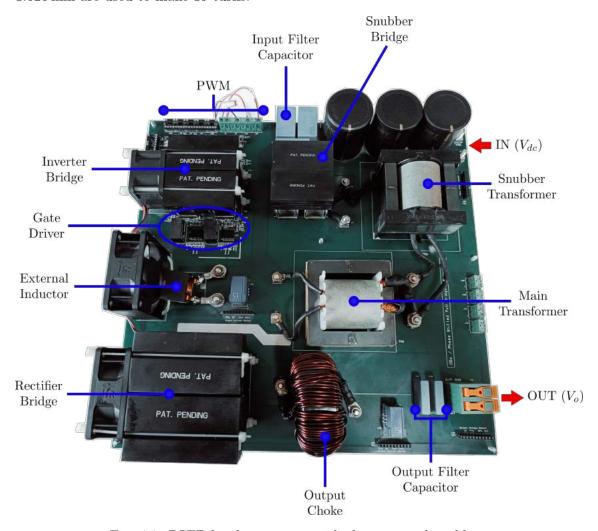

| 4.8  | PSFB hardware setup with the proposed snubber                                                                                                                                                                                                                       | 58  |

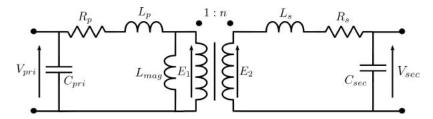

| 5.1  | High-Frequency Transformer Model                                                                                                                                                                                                                                    | 62  |

| 5.2  | Approximate equivalent circuit with open-circuited LV windings. (a) At low frequencies, i.e. the constant slope region in Bode-magnitude plot. (b)                                                                                                                  |     |

| 5.3  | At high frequencies, i.e. around first resonant frequency                                                                                                                                                                                                           | 62  |

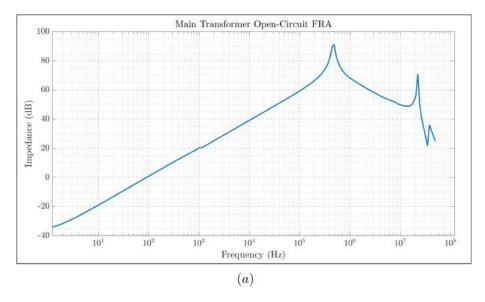

|      | nals. (a) Main transformer impedance. (b) Snubber transformer impedance.                                                                                                                                                                                            | 63  |

| 5.4  | Equivalent circuit with short-circuited LV windings. (a) At low frequen-                                                                                                                                                                                            |     |

|      | cies, i.e. the constant slope region in Bode-magnitude plot. (b) At high                                                                                                                                                                                            | 64  |

| E E  | frequencies, i.e. around first resonant frequency                                                                                                                                                                                                                   | 04  |

| 5.5  | HV input impedance Bode-magnitude plot with shorted LV terminals. (a)  Main transformer impedance. (b) Symbol transformer impedance.                                                                                                                                | 65  |

| 5.6  | Main transformer impedance. (b) Snubber transformer impedance                                                                                                                                                                                                       | 66  |

|      |                                                                                                                                                                                                                                                                     | 67  |

| 5.7  | Series inductor frequency response                                                                                                                                                                                                                                  | 07  |

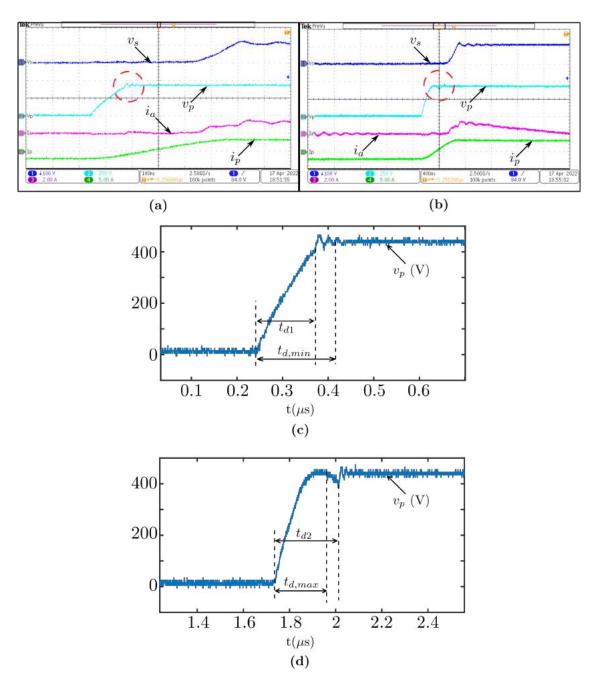

| 5.8  | Converter state variable waveforms at $V_{dc} = 400 \mathrm{V}$ and $P_o = 0.5 \mathrm{kW}$ for                                                                                                                                                                     | 60  |

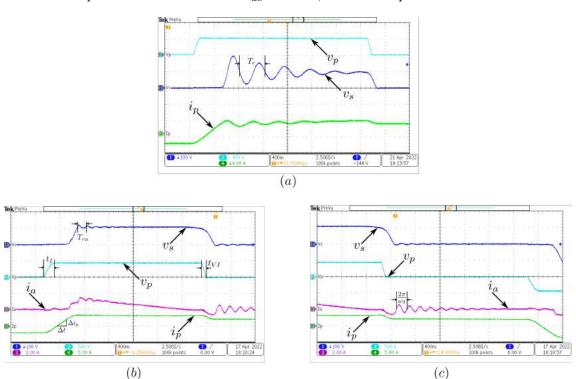

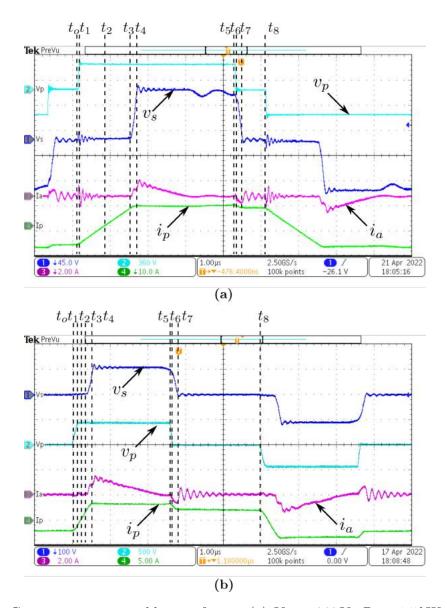

| F 0  | parameter estimation. (a) Without snubber. (b),(c) With proposed snubber                                                                                                                                                                                            | 68  |

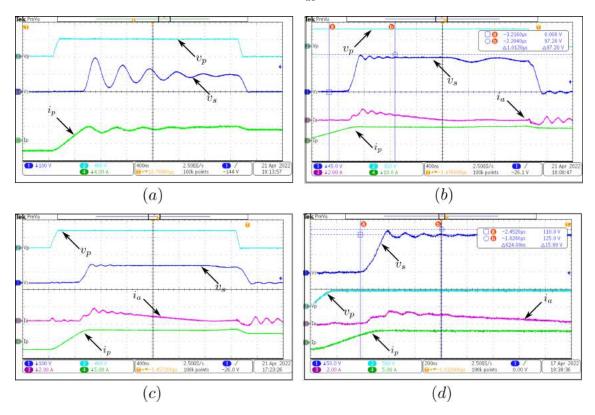

| 5.9  | PSFB waveforms (a) without snubber at $V_{dc} = 400 \mathrm{V}$ (b) with snubber at                                                                                                                                                                                 | 70  |

| F 10 | $V_{dc} = 360 \mathrm{V}$ (c) with snubber at $V_{dc} = 400 \mathrm{V}$ (d) with snubber at $V_{dc} = 440 \mathrm{V}$                                                                                                                                               | 70  |

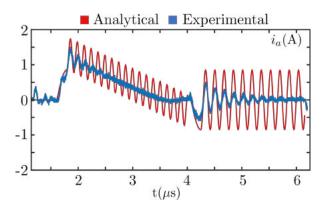

| 5.10 | Analytically obtained snubber current $i_a$ fitted over experimentally mea-                                                                                                                                                                                         | 71  |

| F 11 | sured current                                                                                                                                                                                                                                                       | 71  |

| 5.11 | Converter state variable waveforms. (a) $V_{dc} = 360 \mathrm{V}, P_o = 1.5 \mathrm{kW}$ (b)                                                                                                                                                                        | - 4 |

| F 10 | $V_{dc} = 440 \mathrm{V},  P_o = 0.5 \mathrm{kW}$                                                                                                                                                                                                                   | 74  |

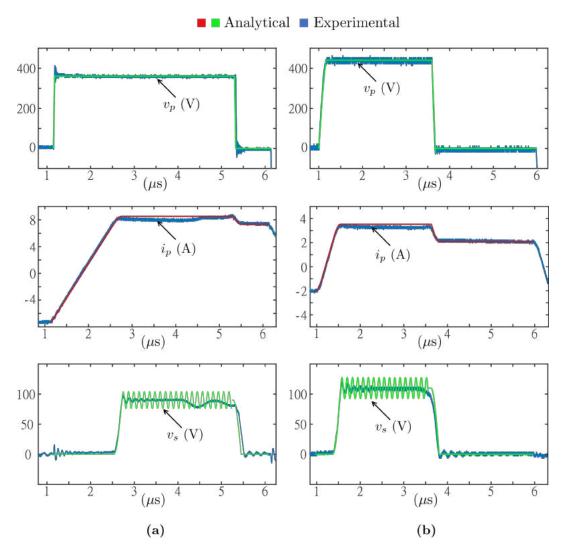

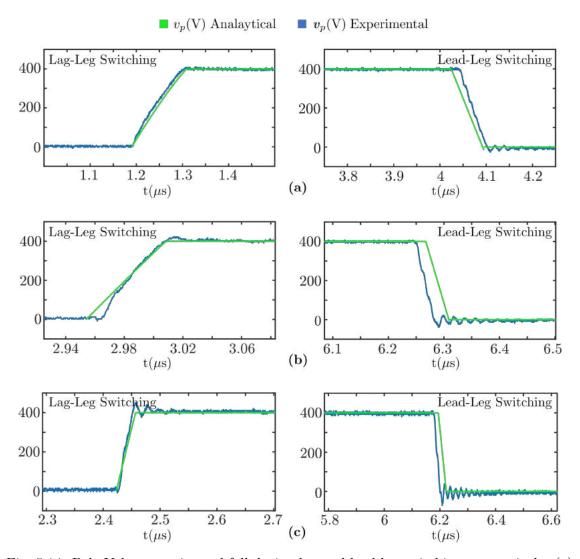

|      | Comparison of analytical and experimental converter waveforms. (a) $V_{dc}=360\mathrm{V},P_o=1.5\mathrm{kW}$ (b) $V_{dc}=440\mathrm{V},P_o=0.5\mathrm{kW}$                                                                                                          | 75  |

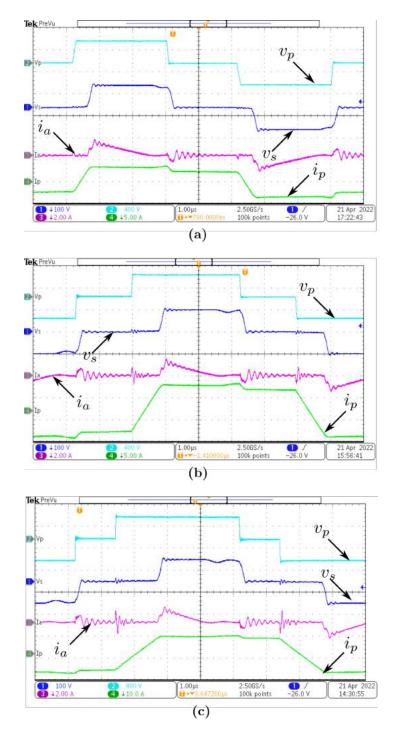

| 5.13 | Converter variables at a DC bus voltage of $400 \mathrm{V}$ . (a) $P_o = 0.5 \mathrm{kW}$ (b)                                                                                                                                                                       |     |

|      | $P_o = 1 \text{kW}  (c)  P_o = 1.5 \text{kW}  \dots  \dots  \dots  \dots  \dots  \dots  \dots$                                                                                                                                                                      | 76  |

| 5.14 | Pole Voltage $v_p$ rise and fall during lag and lead leg switching, respectively.<br>(a) $V_{dc}=400\mathrm{V},\ P_o=0.5\mathrm{kW}$ (b) $V_{dc}=400\mathrm{V},\ P_o=1\mathrm{kW}$ (c) $V_{dc}=400\mathrm{V},$                                                      |     |

|      | $P_0 = 1.5 \mathrm{kW}$                                                                                                                                                                                                                                             | 77  |

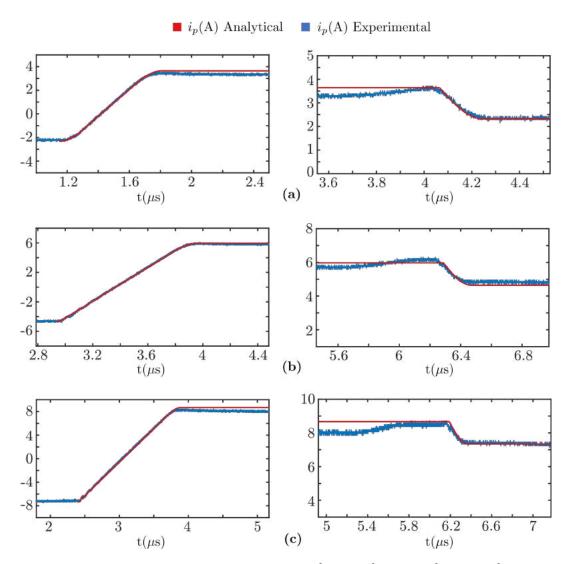

| 5.15 | Primary Current $i_p$ transitions after lag[left plot] and lead[right plot] switch-                               |    |

|------|-------------------------------------------------------------------------------------------------------------------|----|

|      | ing. (a) $V_{dc} = 400 \text{V}$ , $P_o = 0.5 \text{kW}$ (b) $V_{dc} = 400 \text{V}$ , $P_o = 1 \text{kW}$ (c)    |    |

|      | $V_{dc} = 400 \text{V},  P_o = 1.5 \text{kW}$                                                                     | 78 |

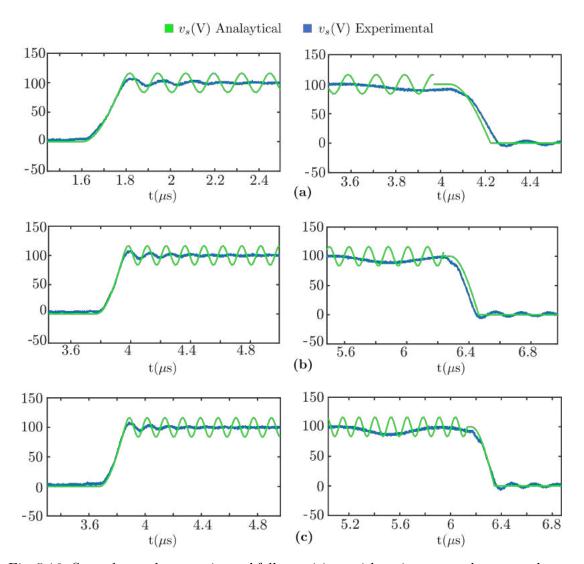

| 5.16 | Secondary voltage $v_s$ rise and fall transitions with active state voltage over-                                 |    |

|      | shoots. (a) $V_{dc} = 400 \text{V}$ , $P_o = 0.5 \text{kW}$ (b) $V_{dc} = 400 \text{V}$ , $P_o = 1 \text{kW}$ (c) |    |

|      | $V_{dc} = 400 \text{V},  P_o = 1.5 \text{kW}$                                                                     | 79 |

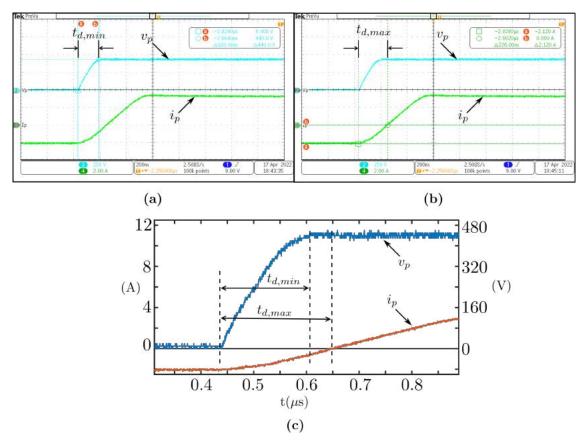

| 5.17 | Pole voltage $v_p$ and primary current $i_p$ waveforms at $V_{dc} = 440 \mathrm{V}$ and                           |    |

|      | $P_o = 0.5 \mathrm{kW}$ . (a) and (b) Measured voltage $v_p$ shows a smooth rise to $V_{dc}$ .                    |    |

|      | The minimum and maximum dead times are marked as $t_{d,min}$ and $t_{d,max}$ ,                                    |    |

|      | respectively. (c) MATLAB plot using experimental data shows the lag-leg                                           |    |

|      | switching transition                                                                                              | 81 |

| 5.18 | Partial ZVS turn ON (a), (c) chosen dead time $t_{d1} < t_{d,min}$ and (b), (d)                                   |    |

|      | $t_{d2} > t_{d,max}$                                                                                              | 82 |

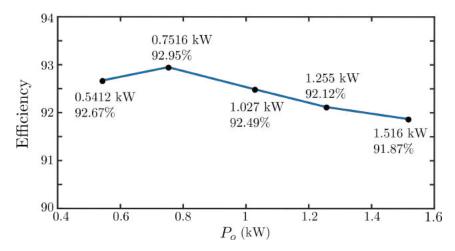

|      | Efficiency v/s Output-Power                                                                                       |    |

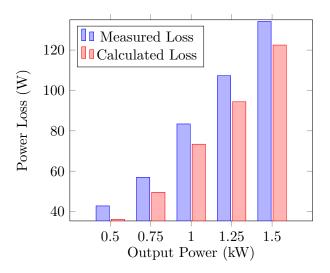

| 5.20 | Measured and calculated loss comparison                                                                           | 86 |

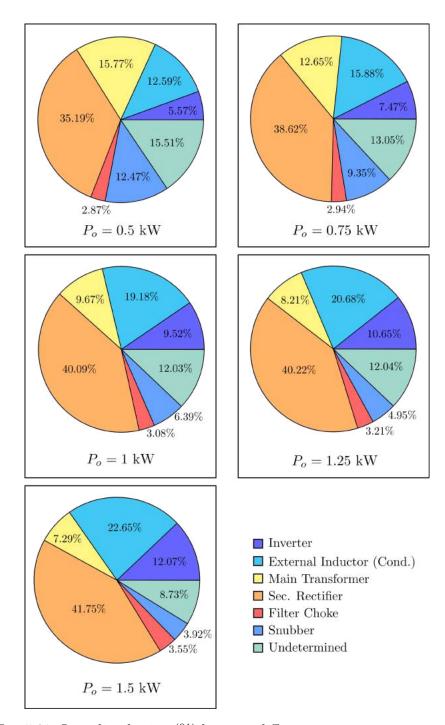

| 5.21 | Loss distribution (%) between different converter components                                                      | 90 |

# Nomenclature

$\Delta I_o$ Output current ripple  $\Delta V_o$ Output voltage ripple  $\Delta V_s'$ Diode bridge voltage overshoot referred to primary δ skin depth Rate of change of magnetising current  $\Delta_{L_m}$  $\Delta_s$ Total rate of change of filter current referred to primary and magnetising current  $\lambda$ Permeance Flux through the transformer core  $\phi$ Resistivity of wire  $\rho$ Cross section of the core  $A_c$ Window are  $A_w$ Filter inductor wire cross section  $a_w$ Peak flux density  $B_m$ Snubber bridge charge equivalent capacitance  $C_{a,Qeq}$  $C_a$ Snubber bridge diode capacitance  $C_{cr}$ Carrier wave  $C_{ctrl}$ Control signal  $C_{d,Qeq}$ Secondary rectifier charge equivalent capacitance  $C_d$ Secondary bridge diode capacitance Parasitic capacitance due to PCBs and heat sinks  $C_{ext}$  $C_f$ Filter capacitance  $C_{oss}$ MOSFET output capacitance  $C_p$ Total primary capacitance Inverter bridge charge equivalent capacitance  $C_{Qeq}$  $C_s$ Sec. diode bridge capacitance referred to primary dApplied duty ratio

- $D_{5-8}$  Secondary bridge diodes

- $D_{a,d}$  Snubber bridge diodes

- $d_{eff}$  Effective duty ratio

- $d_i$  Insulation thickness

- $d_s$  Diameter of a single strand

- $E_i$  Maximum magnetic energy stored in the inductor

- f Frequency of a sinusoidal current

- $f_{eff}$  Effective sinusoidal frequency for non sinusoidal currents

- $f_s$  Switching frequency

- $H_a(x)$  MMF waveform for snubber transformer

- $h_a$  Winding height of snubber transformer

- $H_m(x)$  MMF waveform for main transformer

- $h_m$  Winding height of main transformer

- $i_{ac}$  Current in the secondary of  $T_m$

- $I_m$  Total magnetising current of  $T_m$  and  $T_a$  referred to primary during active mode.

- $i_m$  Total magnetising current of  $T_m$  and  $T_a$  referred to primary

- $I_o$  Output current

- $I_{pk}$  Peak output current

- $I_p$  Primary RMS current

- $i_p$  Primary Current

- $I_s$  Secondary RMS current

- $I_w$  Current flowing in the respective winding

- J Current density

- $K_p$  Peak factor of the output current

- $K_w$  Window utilisation factor

- L Leakage inductance of  $T_m$

- $L_a$  Leakage inductance of snubber transformer

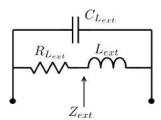

$L_{ext}$  Additional inductance added in series of  $L_{lk}$

$L_f$  Filter inductance

$L_{lk}$  Leakage inductance of  $T_m$  when an external series inductance is added

$L_{m1}$  Magnetising inductance of  $T_m$

$L_{m2}$  Magnetising inductance of  $T_a$

MLT Mean length turn

$mu_o$  Permeability of free space

N Number of turns in filter inductor

n Secondary to primary turns ratio

$N_{pp}$  Number of turns in a single winding portion of primary

$N_p$  Primary turns

$N_{ss}$  Number of turns in a single winding portion of primary

$N_s$  Secondary turns

P' Power for which transformer is designed

$P_{filter}$  Filter inductor losses

$P_{inductor}$  External inductor losses

$P_{inverter}$  Inverter bridge losses

$P_o$  Output power

$P_{rectifier}$  losses

$P_{snubber}$  Snubber losses

$P_{sw}$  Total power loss of a device

$P_{T_m}$  Main transformer losses

$Q_{1-4}$  Inverter switches

$R_{cs}$  Case to sink thermal Resistance

$R_{q,off}$  OFF state gate resistance

$R_{g,on}$  ON state gate resistance

$R_{ic}$  Junction to case thermal resistance

- $R_{load}$  Load Resistance

- $R_{sa}$  Sink to ambient thermal resistance

- $s_{max}$  Number of strands per twist

- $S_T$  Total number of strands per turn of winding

- $T_{amb}$  Ambient temperature

- $T_a$  Snubber Transformer

- $t_{d,max}$  Maximum dead time

- $t_{d,min}$  Minimum dead time

- $T_i$  Junction temperature

- $T_m$  Main Transformer

- $T_{sk}$  Sink temperature

- $T_s$  Switching period

- $v_a$  Pole voltage of snubber bridge

- $V_{dc}$  Input DC bus voltage

- $V_o$  Output DC voltage

- $v_p$  Pole voltage

- $v_{s'}$  Voltage  $v_s$  referred to primary

- $v_s$  Transformer secondary voltage

- $w_p$  primary winding conductor cross-section

- $w_s$  Secondary winding conductor cross-section

# Introduction

# 1.1 Background and Motivation

Power Electronic Converters (PECs) are indispensable part of renewable energy integration, automotive industry and traction, telecom power supplies, and energy storage systems. For instance, a PEC utilises AC power to charge a battery by converting AC into DC. Moreover, this PEC controls its charging to avoid any premature battery failure. PECs are desired to be low-cost, highly efficient, smaller in size, and meet electric safety requirements.

Recent developments in Wide Band Gap (WBG) devices have influenced engineers to build even higher power-density converters at reduced costs. Thanks to their wide bandgap between the valence and the conduction band that allows high-frequency switching at higher voltages and temperatures [1].

Pushing to higher switching frequencies minimises the size of magnetics but results in higher switching losses and noise due to electromagnetic interference (EMI). Thus, there is a necessity to reduce these switching losses in PECs.

#### 1.2 Isolated Unidirectional DC-DC Converters

In many power electronics applications, it is desired to integrate an isolation transformer into the switching converter for the following reasons [2].

- The input and output of galvanically isolated power supplies do not share a common ground, breaking the ground loops.

- Better optimisation when a large step-down or step-up conversion ratio is required.

- A converter can obtain multiple outputs by adding multiple secondary windings in the transformer.

These isolated converters can be categorised as uni- or bi-directional, depending on the direction of the power flow. The power flows from source to load in a unidirectional converter, while it flows in either direction in another. Unidirectional isolated DC-DC converters have a wide range of applications, including telecom and server power supplies, electric vehicle chargers, fuel cells, and solar PV grid integration [3].

Many isolated unidirectional converter topologies have been proposed in the literature. Converters like flyback, forward, and isolated versions of Cuk and SEPIC are used in low-voltage, and low-power applications [2,4–6]. Traditional Pulse Width Modulated (PWM)

converters are used in high voltage and high power applications but are hard-switched and have high EMI. Essentially a PWM converter, Phase-Shifted Full-Bridge (PSFB) is an isolated version of the buck converter used in most high-power (>1 kW) applications. The PSFB allows soft-switching of the inverter switches and therefore has lesser EMI issues [7,8]. However, the soft-switching in a PSFB is lost at low loads. Resonant-based power converters such as LLC can achieve soft-switching over the entire load range. However, LLC requires variable frequency operations making filter design and control complicated. The gain is also essentially load-dependent in resonant converters [9]. Another limitation of LLC-based converters is their ability to achieve a narrow range of converter gain. Dual-Active-Bridge based DC-DC converter achieves a wide gain range and soft-switching over a wide operating condition [10]. DAB also operates at a constant switching frequency. But both LLC and DAB incur higher conduction loss when compared with PSFB. As PSFB has a relatively simple modulation and control strategy, it is still used in most applications.

# 1.3 Phase-Shifted Full-Bridge

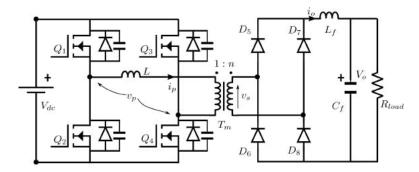

Fig. 1.1: Phase-Shifted Full-Bridge Converter

A PSFB Converter is one of the most widely used soft-switching topologies in industry applications [11,12]. The phase-shifted PWM control scheme helps achieve Zero Voltage Switching (ZVS) of the primary bridge using circuit parasitics. The turning ON of the switches when the switch voltage is zero leads to a lossless switching known as zero voltage switching. It allows accomplishing high operating frequencies with high power densities and reduced EMI.

Fig 1.1 shows a PSFB converter consisting of an inverter bridge, a transformer  $T_m$  to provide galvanic isolation and required voltage amplification, a rectifier bridge and an output filter. Using phase-shifted PWM control, the magnetic energy stored in the inductance L charges and discharges the output capacitances of the inverter leg during the dead time between the associated gate signals of the complementary switch pair. Inductance L could be the leakage inductance  $L_{lk}$  of  $T_m$  or a series combination of  $L_{lk}$  and an additional inductor  $L_{ext}$ .

#### **PSFB** Modulation Strategy:

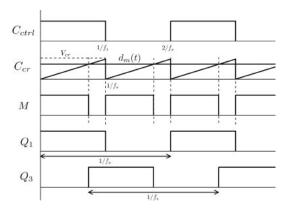

Consider a control signal  $C_{ctrl}$  with a 50% duty ratio of frequency  $f_s/2$  and a positive slope uni-polar saw-tooth carrier wave  $C_{cr}$  of frequency  $f_s$ . Comparing  $C_{cr}$  with a modulation signal  $d_m(t) = d \times V_{cr}$  generates a signal M.  $V_{cr}$  is the peak of the signal  $C_{cr}$  and d is the required duty ratio. The gating signals for the switches are thus derived as follows.

$$Q_1 = C_{ctrl}$$

$$Q_2 = \overline{Q_1}$$

$$Q_3 = C_{ctrl} \otimes M$$

$$Q_4 = \overline{Q_3}$$

The modulation strategy is shown in Fig 1.2. Thus, both legs of the bridge operate

Fig. 1.2: PSFB modulation strategy

with a 50% duty. The phase between the two legs is controlled to achieve desired gain. The converter has two operational states: active and zero. The power is transferred from the source to load during active mode and freewheels in the converter during the passive mode [13]. The two legs of the inverter look symmetrical, but the phase-shift control introduces an asymmetry due to which the two legs behave differently during the switching transitions. The leg switching from active to zero state is called the leading leg, while the one switching from zero to the active state is called the lagging leg [14].

However with all the advantages of the PSFB, it suffers from a few limitations of severe voltage overshoots in the secondary, narrow ZVS range, large duty cycle loss, and conduction losses during free-wheeling [15].

# 1.4 The Problem of Secondary Voltage Overshoots

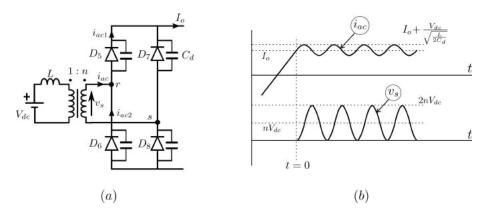

Consider the PSFB equivalent model shown in Fig 1.3(a). The parasitic capacitance of

Fig. 1.3: (a) Rectifier bridge during active mode. (b) Rectifier voltage overshoot waveforms.

the diodes shown is  $C_d$ . Assume the the voltage  $v'_p = +V_{dc}$  and  $v_s = 0$  before t = 0. The current  $i_{ac}$  is  $+v_e$  but less than the load current  $I_o$ . The current  $i_{ac1}$  and  $i_{ac2}$  are given as follows.

$$i_{ac1} = \frac{I_o + i_{ac}}{2} \tag{1.1}$$

$$i_{ac2} = \frac{I_o - i_{ac}}{2} \tag{1.2}$$

(1.1) and (1.2) show that the two currents  $i_{ac1}$  and  $i_{ac2}$  are +ve therefore, all diodes of the rectifier are in conduction. The current  $i_{ac}$  rises linearly at a rate of  $V_{dc}/nL$  As<sup>-1</sup>. As  $i_{ac}$  reaches  $I_o$ ,  $i_{ac1} = I_o$  and  $i_{ac2} = 0$ , diodes  $D_6$  and  $D_7$  stop conducting and get reverse biased. As  $i_{ac}$  increases further and the  $i_{a2}$  becomes negative, diode capacitances of  $D_6$  and  $D_7$  show up to form a resonant circuit with  $n^2L$ . Solving the equivalent circuit gives

$$n^2 L \frac{di_{ac}(t)}{dt} = nV_{dc} - v_s$$

$$2C_d \frac{dv_s(t)}{dt} = i_{ac} - I_o$$

Using the above equations, we get

$$2n^{2}LC_{d}\frac{d^{2}v_{s}(t)}{dt^{2}} = nV_{dc} - v_{s}$$

(1.3)

Solving the differential equation (1.3),  $v_s$  and  $i_{ac}$  can be expressed as

$$v_s(t) = nV_{dc} \left\{ 1 - \cos\left(\frac{1}{\sqrt{2n^2LC_d}}t\right) \right\}$$

(1.4)

$$i_{ac}(t) = \frac{V_{dc}}{\sqrt{\frac{L}{2C_d}}} \sin\left(\frac{1}{\sqrt{2n^2LC_d}}t\right)$$

(1.5)

Equation (1.4) and Fig 1.3(b) show that the rectifier voltage overshoots can go up to twice the secondary referred DC bus voltage  $V_{dc}$ . Thus, it increases the voltage rating of rectifier diodes and makes them susceptible to overvoltage breakdown.

# 1.5 Existing Snubber Solutions

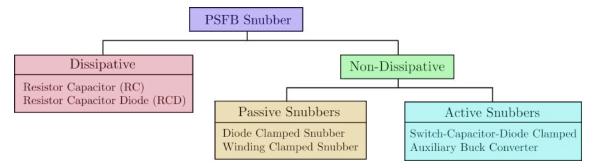

Several remedies (snubbers) have been proposed in the literature to mitigate the secondary bridge voltage overshoots. These snubbers can broadly be classified as shown in Fig 1.4. Fig 1.5 shows a PSFB converter with some widely used snubber circuits.  $L_{lk}$  is the leakage

Fig. 1.4: Classification of snubbers for Phase-Shifted Full-Bridge

inductance of the transformer  $T_m$ , and  $L_{ext}$  represents the externally added inductor and can be zero or have a finite value.

The following section briefly discusses some popular snubber topologies and their respective advantages and limitations. Active snubbers are usually a combination of passive elements like capacitance, inductance and diodes with an active element, i.e. a switch.

#### Resistor-Capacitor (RC)

The traditional RC circuit across the rectifier diodes can dampen the voltage overshoots across the rectifier bridge. However, the total excess energy is lost in the damping resistor.

#### Resistor-Capacitor-Diode (RCD)

An alternative solution can be a RCD snubber [16]. The RCD clamped snubber is composed of  $C_{snb}$ ,  $D_{snb}$ , and  $R_{snb}$ , as shown in Fig 1.5(b).  $C_{snb}$  is large enough to be assumed as a constant voltage source  $V_c$ . As  $v_s$  reaches  $V_c$ ,  $D_{snb}$  gets forward biased, clamping  $v_s$  at  $V_c$ . The excess current flows through the snubber capacitance  $C_{snb}$ . Resistance  $R_{snb}$  provides the discharge path for the charge balance of  $C_{snb}$ . A portion of this energy gets transferred to the load, and the rest is lost in  $R_{snb}$ .

The advantage of using an RCD snubber is its simple design and no requirement of additional circuitry. However, this too turns out to be an inefficient solution for high-voltage and high-power converters.

Fig. 1.5: PSFB converter with some popular snubber topologies. (a) Highlighted snubber positions. (b) RCD (c) Diode-Clamped Snubber (d) Winding-Clamped (e) Switch-Diode-Clamped (f) Auxiliary Buck Converter

#### Switch-Diode-Clamped

A non-dissipative Switch-Capacitor-Diode Clamped snubber 1.5(e) proposed in [17] replaces the resistive path of the RCD snubber with a switch  $S_{snb}$  to discharge  $C_{snb}$ . As voltage  $v_s$  reaches  $V_c$ ,  $D_{snb}$  gets forward biased, and the excess current flows through the clamping capacitor. This extra charge stored in  $C_{snb}$  is transferred to the load by turning

ON the snubber switch  $S_{snb}$  as shown in [17] and [18].

#### Auxiliary Buck Converter (Non-Dissipative, Active Snubber)

The proposed Auxiliary Buck Converter snubber circuits in [19–21] clamp the secondary voltage  $v_s$  to  $V_c$  through  $D_{snb}$  and  $C_{snb}$ , similar to switch-capacitor-clamped snubber. The difference lies in the clamping capacitor discharging strategy. These solutions propose an auxiliary buck converter operating in discontinuous and boundary conduction mode to create a path for charge balancing of  $C_{snb}$  as shown in Fig 1.5(f).

The active snubbers effectively clamp the diode bridge voltage overshoots to a clamping voltage  $V_c$ . These lossless and regenerative snubbers are efficacious in clamping the oscillations due to both  $L_{ext}$  and  $L_{lk}$ . However, they suffer from the following drawbacks.

- A complex control scheme for clamping capacitor charge balancing.

- An auxiliary gate driver circuitry increases the component count and decreases system reliability.

- The switch  $S_{snb}$  in many of these snubbers is hard-switched, leading to switching loss in the snubber. Although [17, 18] shows a strategy to ZVS turn ON  $S_{snb}$ , but with a complex control scheme.

## Diode-Clamped Snubber

Transformer leakage  $L_{lk}$  (primary winding + secondary winding) and an external inductor  $L_{ext}$  to achieve ZVS. To reduce the inductor losses,  $L_{ext}$  is either put in the primary or the secondary, whichever has the lower current.

A diode-clamped solution is proposed in [14] that uses a resonant inductor  $L_{ext}$  and clamping diodes  $D_{snb}$ , keeping the transformer leakage inductance as low as possible. The clamping diodes fix the common point X of  $L_{ext}$  and the transformer terminal to the input DC bus, as shown in Fig 1.5(c). The other terminals of  $T_m$  and  $L_{ext}$  are connected to the lagging and leading leg, respectively.

Some significant advantages of this non-dissipative snubber are its design simplicity and low component count. However, it suffers from the following limitations.

- $D_{snb}$  conducts twice in half the switching cycle, i.e. during the active and the passive states, increasing the conduction and switching losses in the diodes. However, its conduction is unnecessary during the zero states as the clamping action is only required during the active mode.

- It increases the current flowing through the resonant inductor  $L_{ext}$  during the free-wheeling interval, causing additional conduction loss.

- It only clamps oscillations due to  $L_{ext}$  but oscillations caused by  $L_{lk}$  remain. Therefore, it necessitates to add  $L_{ext}$  and minimising the leakage inductance  $L_{lk}$ . Thus,

restricting the inductance necessary for soft-switching to be integrated into the transformer.

The Improved Diode-Clamped solution in [22] proposes two clamping diodes  $D_{snb}$  connected to a common point X. However, the lagging and leading legs are interchanged, so  $T_m$  and  $L_{ext}$  are connected to the leading and lagging legs, respectively.

With this simple modification,  $D_{snb}$  conducts only once in half the switching cycle, i.e. during the active state. A lower current than [14] flows through  $L_{ext}$  during the zero state. Thus, improving the overall efficiency of the converter. However, the problem of the necessity of resonant inductor and the voltage overshoot due to  $L_{lk}$  remains.

#### Winding-Clamped Snubber

The winding clamped snubber in [23, 24] consists of an integrated tertiary winding and a resonant capacitor  $C_{rr}$  parallel to the third winding as shown in Fig 1.5(c). The primary to tertiary winding ratio is  $N_1/N_3 = k_a$ . The additional winding clamps the secondary transformer voltage to  $nk_aaV_{dc}$  through a diode bridge rectifier during the active mode. Unlike the diode-clamped snubber, the snubber bridge diodes conduct only once every half switching cycle. This snubber takes care of the ringing due to the primary winding's leakage inductance. However, the secondary winding leakage inductance still rings with the parasitic capacitance of the diode bridge.

The non-dissipative passive snubbers discussed in this section do not reduce the ringing due to all the inductances  $L_{lk}$  (primary and secondary) and  $L_{ext}$ . Thus, the problem remains either due to a necessity for  $L_{ext}$  or in applications of higher load voltages.

#### 1.6 Contribution of the Thesis

The previous sections discussed the issue of rectifier bridge voltage overshoot in a PSFB converter and some popular remedies proposed in the literature. The thesis presents a novel snubber to overcome the limitations of these solutions and design a PSFB converter and the proposed snubber for a given specification.

#### 1.6.1 The Proposed Snubber

A PSFB snubber is desired to have the following features.

- It should effectively reduce/clamp the diode bridge voltage overshoots.

- It should be non-dissipative and regenerative.

- It must have minimum to zero active switches to improve the reliability of the snubber and add minimum auxiliary components.

- Should not have complex control such as what is required for charge balancing of clamping capacitor.

• It should provide an option to integrate the resonant inductor in the transformer.

With these features in mind, this thesis proposes a novel passive regenerative snubber. The topology comprises a snubber transformer  $T_a$  and a snubber diode bridge which clamps the secondary of the power/main transformer  $T_m$  to the DC bus voltage through  $T_a$ .

#### 1.6.2 PSFB Design

The manuscript presents a detailed discussion of the converter operation with the novel snubber. The circuit analysis considers and models all the major parasitics like junction capacitances, leakage and magnetising inductances.

It then lays down a detailed design procedure for a phase-shifted full-bridge converter and the proposed snubber with a wide range of operating conditions considering line (input voltage) and load regulation. The design ensures the converter gain and ZVS turn-on of the switches in each operating condition. The converter operation is validated experimentally on a hardware prototype of a  $360\,\mathrm{V} - 440\,\mathrm{V}/48\,\mathrm{V}$  and  $1.5\,\mathrm{kW}$  step-down PSFB converter.

# 1.7 Organisation of the Thesis

A brief chapter-wise summary is presented as follows.

Chapter 2: Phase-Shifted Full-Bridge Analysis provides a comprehensive circuit analysis of the PSFB converter with the proposed snubber. The study obtains closed-form expressions for the converter state variables considering all the dominant circuit parasitics.

Chapter 3: Phase-Shifted Full-Bridge Design presents a detailed design procedure of the converter for the given specifications. The converter gain expression obtained in Chapter 2 is utilised to determine the transformer turns ratio and required leakage inductance to achieve ZVS turn-ON.

Chapter 4: Hardware Design discusses the design of magnetics and components selection.

Chapter 5: Experimental Verification The snubber topology and converter design are validated on a hardware prototype of 360 V - 440 V/48 V and 0.5 - 1.5 kW. The final section of the chapter presents the loss distribution and overall efficiency calculations.

Chapter 6: Conclusions and future work This chapter summarizes the overall contribution of the work presented in this thesis. An outline of the future work is also given.

# Phase-Shifted Full-Bridge Analysis

## 2.1 Introduction

In Chapter 1, we discussed the motivation and focus of the thesis. The simplicity of PSFB operation makes it a popular topology in medium to high voltage and power applications. However, the diode bridge voltage overshoots remain one of the major drawbacks of the converter. We discussed various solutions available in the literature and their limitations. Chapter 1 then proposes a novel passive regenerative snubber topology to overcome some of the constraints posed by the existing snubbers.

This chapter covers a detailed analysis of the PSFB converter and the proposed snubber considering all the dominant parasitics like the transformer's leakage inductances and junction capacitance of the diodes. The converter operation can be divided into eight topological stages. These eight operation modes are analysed by solving their specific equivalent circuits and deriving closed-form expressions for the state variables during the modes. The conditions required for a successful zero voltage switching are derived.

The obtained closed-form expressions in each mode are then used to determine the converter gain. This expression will help design the PSFB in Chapter 3. The chapter also presents a detailed discussion on deviations from the idealities assumed during the analysis.

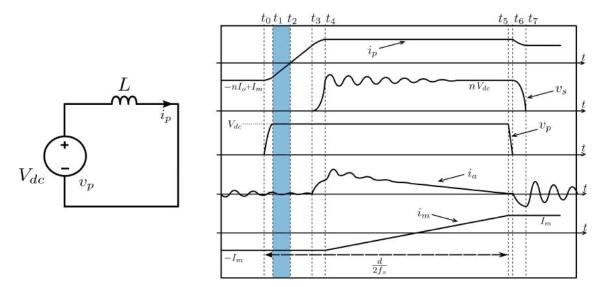

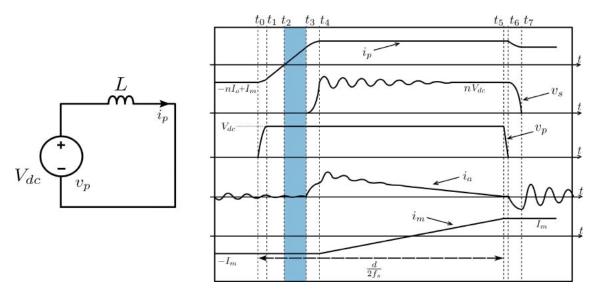

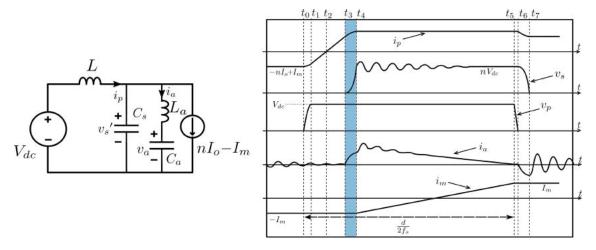

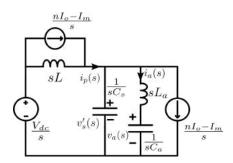

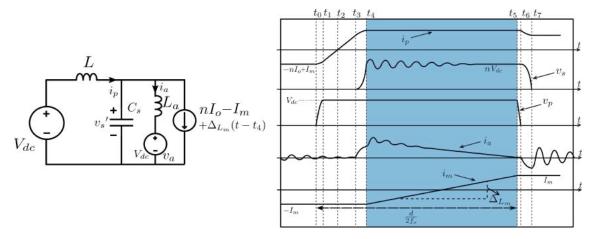

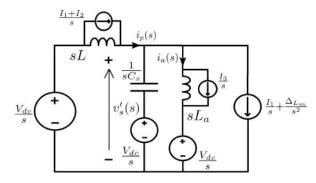

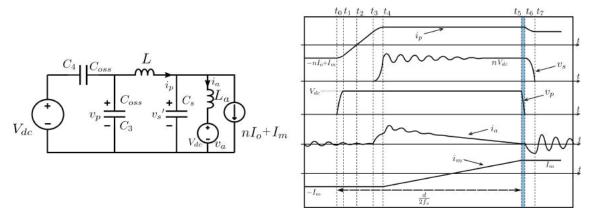

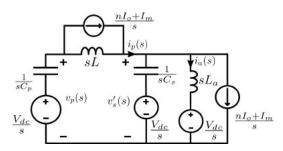

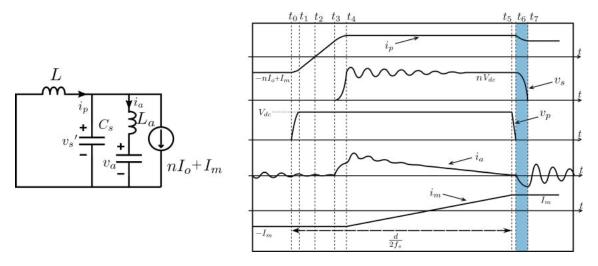

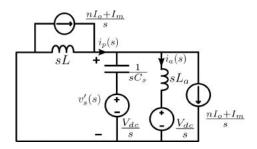

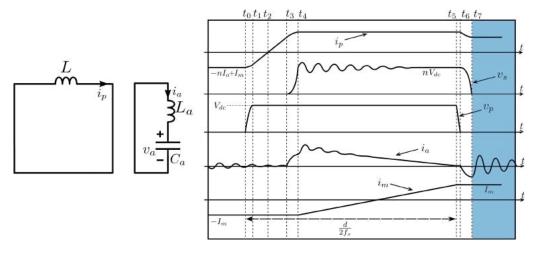

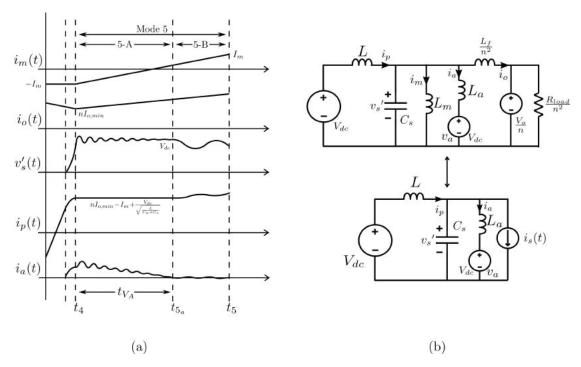

# 2.2 Operational Analysis

Fig 2.1 shows the PSFB converter with the proposed snubber.  $C_{oss}$ ,  $C_d$ , and  $C_a$  are the output and junction capacitances of the MOSFETs, secondary, and snubber diodes, respectively. Inductances L and  $L_a$  are the leakage inductances of the main transformer  $T_m$

Fig. 2.1: PSFB converter with the proposed snubber.

Fig. 2.2: Converter waveforms for a half-switching cycle.