# Carrier-Based Implementation of SVPWM for Dual Two-Level VSI and Dual Matrix Converter With Zero Common-Mode Voltage

1

# Carrier based implementation of SVPWM for dual two-level VSI and dual matrix converter with zero common-mode voltage

Rohit Baranwal, Student Member, IEEE, Kaushik Basu, Member, IEEE and Ned Mohan, Life Fellow, IEEE

Abstract—PWM converters generate switching common-mode voltages across the load terminals. These voltages cause commonmode currents, leading to bearing failure in motor loads and EMI problems. This paper presents a generalized carrier based PWM technique for open-end winding motor drives that completely eliminates switching common-mode voltage. The proposed method is applicable to both dual two-level voltage source inverter (VSI) and dual matrix converter based open-end winding drives. Detailed analysis shows that the carrier based method requires significantly less computation compared to the corresponding space vector implementation. This paper also outlines the relationship between the two implementations. The carrier based method is shown to achieve superior performance in terms of resource requirements and execution time when implemented on an FPGA based real time control platform. Simulation and experimental results have been presented to validate the proposed method.

Index Terms—Pulse Width Modulation (PWM), Open-end winding drive, Carrier based Modulation, Dual two-level inverter, Dual matrix converter, Common-mode voltage, AC motor drive

#### I. INTRODUCTION

Pulse width modulation (PWM) is the most commonly used switching technique for synthesizing adjustable magnitude and frequency AC due to reasons such as higher quality of the output voltage waveform, reduced filter requirement and faster dynamic response. However, conventional PWM techniques for DC/AC two-level voltage source inverters (VSI) and three phase AC/AC matrix converters (MC) cause high frequency common-mode voltage at the load terminals [1]-[5]. In case of a motor load, this can cause common-mode currents to flow through the motor bearings due to electrostatic coupling through parasitic capacitance. This leads to premature failure of motor bearings and undesirable electromagnetic interference (EMI). Passive common-mode filters are employed for impeding these common-mode currents [6]-[8]. Due to the use of additional filter components, this solution leads to reduced power density and reliability along with additional cost. PWM techniques have been proposed in the literature, both for VSI and MC, for the suppression of switching common-mode voltage [9], [10]. It can however, cause a reduction in the quality of the output voltage waveform and achievable maximum voltage transfer ratio [11]. Multilevel converters have also been explored for common-mode voltage elimination: for example [12], [13] for three level neutral point clamped converter (NPC), [14] for five level NPC and [15] for cascaded multilevel inverters.

Open-end winding drives consisting of two inverters are an alternative to NPC and cascaded multilevel inverters to gain more voltage levels in the output voltage waveform. An openend winding drive was proposed in [16] and some more openend winding drive configurations have been presented in [17] and [18]. Open-end winding drives not only give more voltage levels in the output, but the maximum output voltage for a given input voltage is more than that for a single converter. In addition, they can be controlled to eliminate common-mode voltage across the load. In [19], a space vector PWM technique has been presented for an open-end winding two-level voltage source inverter (VSI) drive to eliminate switching commonmode voltage across the load. In [20], a two winding induction machine drive with dual two-level inverters is presented with a PWM method featuring common-mode voltage elimination as well. The idea of open-end winding drives has been extended to matrix converters in [21], where a dual matrix converter drive with common-mode voltage elimination and grid power factor control is presented. Dual multilevel converters for open-end winding drives with modulation strategies to eliminate common-mode voltage have also been proposed in the literature [22]–[27].

The PWM techniques presented in references [9]–[27] use space vector implementation, except the sine PWM method in [13]. As an alternative to space vector approach, carrier based techniques are capable of producing same results as space vector based approaches, as concluded in [28]. In comparison with space vector modulation, carrier based techniques can require less computation and result in simple implementation, as seen in [29]. They also give an insight into the relation between the duty ratios for converter switches and the reference output voltages and input voltages. A carrier based approach for space vector PWM for two-level inverter has been presented in [29]. It is based on simple comparisons of the reference output voltage waveforms rather than computation of the reference output voltage space vector along with the sector identification process required by space vector approach. In [30] and [31], carrier based PWM methods for matrix converters have been presented. Carrier based PWM techniques for multilevel and multiphase (more than three phases) inverters have been explored as well [32]–[35]. Carrier based approaches have been studied together with space vector based approaches to observe relations between them and to compare them [35]–[37].

The SVPWM techniques with common-mode voltage suppression for dual VSI and dual MC have been proposed and developed in isolation. However, there are similarities in the PWM control of these two converters. A carrier based implementation for the PWM control of the open-end winding dual two-level VSI drive has been presented in [38]. In this paper, the similarities between the PWM control of dual VSI and dual MC with common-mode voltage suppression are identified. Then, a generalized carrier based PWM technique for openend winding drive that includes both dual VSI and dual MC as the power converter has been presented. The generalized algorithm presented in this paper results in the computation of the duty cycle of each of the switches directly from the sensed input voltage and reference output voltage waveforms. There are no trigonometric and square root operations involved in any computation required for the proposed algorithm as opposed to the space vector approach. Overall, the carrier based algorithm requires significantly less computation. Both space vector based and carrier based algorithms have been implemented on an FPGA based platform to compare resource requirement and the speed of computation. Simulation and experimental results have been presented to demonstrate the working of the carrier based algorithm.

The paper is structured in a total of eight sections. Section II describes the dual converters and the space vectors to be used for PWM. The discussion in the section III gives the similarities between the two-level and matrix converter cases and defines a general notation for the two platforms. In section IV, the carrier based algorithm has been derived which is then compared to the space vector based approach in section V. The simulation and experimental results are presented in section VI and section VII respectively. The conclusions are presented in the last section.

### II. DUAL MATRIX CONVERTER, DUAL VSI AND SYNCHRONOUS ROTATING VECTORS

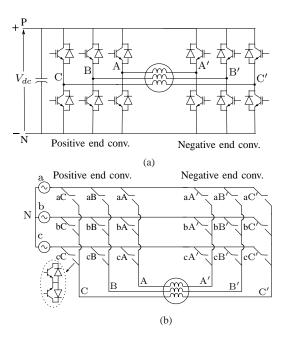

A dual converter consists of two converters of a given type, with one converter connected to each side of an open-end winding three phase load. A dual two-level inverter is shown in Fig. 1(a) and a dual matrix converter system is shown in Fig.1(b). In both systems, one converter is named positive end converter and the other is named negative end converter. The dual two-level inverter has two two-level voltage source inverters (VSI) while the dual matrix converter has two matrix converters.

The space vector of positive end converter (for both dual VSI and dual matrix converter) is defined in (1).

$$\mathbf{U} = v_{\rm AN} + v_{\rm BN} e^{j\frac{2\pi}{3}} + v_{\rm BN} e^{j\frac{-2\pi}{3}} \tag{1}$$

The voltages  $v_{\rm AN},\,v_{\rm BN}$  and  $v_{\rm CN}$  are voltages of positive end output terminals A, B and C respectively wrt a point N. The point N is the negative terminal of the dc bus in the case of dual two-level inverter. In the case of dual matrix converter, the point N is the neutral point of the input three phase ac voltage.

A two-level VSI can synthesize three phase ac output of adjustable amplitude and frequency from a dc voltage. There are a total of six switches (realized by six IGBTs). The upper and the lower switches in one leg are switched in

Fig. 1. (a) Dual two-level inverter (b) Dual matrix converter

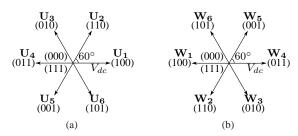

Fig. 2. Two-level VSI Space vectors (a) Positive end Space vectors (b) Negative end space vectors

complimentary fashion. So, there are eight total combinations, thus forming eight voltage space vectors. Six of these are active vectors while rest two have zero magnitude and are called zero vectors. These vectors are shown in Fig. 2(a). Each of the six active vectors are of magnitude  $V_{dc}$  i.e. the dc bus voltage and are fixed in position. As an example when terminal A of the load is connected to dc bus terminal P and load terminals B and C are connected to dc bus terminal N, the switching state (100) is obtained. Thus the vector  $\mathbf{U_1}$  is synthesized.

A matrix converter can synthesize three phase ac voltage of adjustable frequency and amplitude from a three phase ac voltage source. The converter consists of nine switches (realized with eighteen IGBTs), forming three legs. Each of these three legs can be in three different positions, resulting in twenty-seven total switching states. Thus there are twenty-seven voltage space vectors for a matrix converter. Out of these twenty seven space vectors, three vectors are zero vectors and eighteen vectors are stationary but of varying magnitude in time. These eighteen stationary vectors along with the three zero vectors are used in the indirect matrix converter modulation technique [39]. The remaining six vectors have a constant magnitude of  $\frac{3}{2}V_i$  ( $V_i$  is input peak phase voltage) but keep rotating uniformly and are known as synchronously rotating space vectors. Three of these rotate in counter-

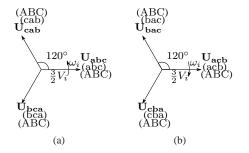

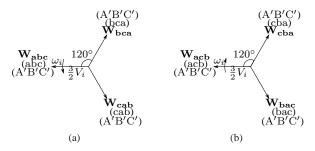

Fig. 3. Synchronously rotating vectors for positive end matrix converter (a) CCW Vectors (b) CW Vectors

Fig. 4. Synchronously rotating vectors for negative end matrix converter (a) CCW vectors (b) CW Vectors

clockwise direction with the input frequency  $\omega_i$  and are called counter-clockwise (CCW) vectors. The remaining three rotate in clockwise direction with the input frequency  $\omega_i$  and are known as clockwise (CW) space vectors. The CCW and CW vectors for the positive end matrix converter are shown in Fig. 3(a) and Fig. 3(b) respectively. As an example, the switching state (cab) implies that the load terminals A, B and C are connected to source terminals c, a and b respectively. This is done by turning ON switches cA, aB and bC and thus the vector  $\mathbf{U_{cab}}$  is applied. Similarly, the other vectors are formed.

The space vectors for the negative end VSI are shown in Fig. 2(b). Note that the space vectors of the negative end VSI are opposite in direction of those of corresponding positive end VSI space vectors. Similarly, the CCW and CW vectors for the negative end matrix converter are shown in Fig. 4(a) and Fig. 4(b) respectively. These are opposite in direction to the CCW and CW vectors of the positive end matrix converter. The space vector of negative end converter (for both dual VSI and dual matrix converter) is defined in (2).

$$\mathbf{W} = -(v_{A'N} + v_{B'N}e^{j\frac{2\pi}{3}} + v_{C'N}e^{-j\frac{2\pi}{3}})$$

(2)

The voltages  $v_{\rm A'N}$ ,  $v_{\rm B'N}$  and  $v_{\rm C'N}$  are voltages of negative end output terminals A', B' and C' respectively wrt a point N. The point N is the negative terminal of the dc bus in the case of dual two-level inverter and the neutral point of the input three phase ac voltage in the case of dual matrix converter.

For the negative end VSI, when load terminal A' is connected to dc bus terminal P and load terminal B' and C' are connected to dc bus terminal N, the vector  $\mathbf{W_1}$  is synthesized. Similarly, for the negative end matrix converter, when the load terminals A', B' and C' of the load are connected to terminals c, a and b of the source respectively, vector  $\mathbf{W_{cab}}$  is synthesized. The other vectors are formed likewise.

The common-mode voltage at the load terminals is defined

by (3).

$$v_{\text{com,pos}} = \frac{v_{\text{AN}} + v_{\text{BN}} + v_{\text{CN}}}{3}$$

$$v_{\text{com,neg}} = \frac{v_{\text{A'N}} + v_{\text{B'N}} + v_{\text{C'N}}}{3}$$

(3)

The differential common-mode voltage  $v_{\rm com,diff}$  defined in (4) is what affects circulating currents in open-end winding drives, as explained in [40]. The average of these common-mode voltages defined (5) is what affects EMI, as explained in [1].

$$v_{\text{com,diff}} = v_{\text{com,pos}} - v_{\text{com,neg}}$$

(4)

$$v_{\text{com,sum}} = \frac{v_{\text{com,pos}} + v_{\text{com,neg}}}{2}$$

(5)

Based on these expressions, for the two-level VSI, vectors  $\mathbf{U_1},\ \mathbf{U_3},\ \mathbf{U_5},\ \mathbf{W_1},\ \mathbf{W_3}$  and  $\mathbf{W_5}$  have a common-mode voltage  $\frac{V_{dc}}{3}$ . The vectors  $\mathbf{U_2},\ \mathbf{U_4},\ \mathbf{U_6},\ \mathbf{W_2},\ \mathbf{W_4}$  and  $\mathbf{W_6}$  have common-mode voltage of  $\frac{2V_{dc}}{3}$ .

Thus, the set  $U_1$ ,  $U_3$   $U_5$ ,  $W_1$ ,  $W_3$  and  $W_5$  can be used for converter control so that the common-mode voltage across the load  $v_{\rm com,diff}$  is zero and the average of the commonmode voltages  $v_{\rm com,sum}$  is constant at  $\frac{V_{dc}^{-}}{3}$ . The other set of vectors  ${\bf U_2},\,{\bf U_4}\,{\bf U_6},\,{\bf W_2},\,{\bf W_4}$  and  ${\bf W_6}$  can also be used to achieve zero differential common-mode voltage  $v_{\rm com,diff}$ , while keeping the average  $v_{\text{com,sum}}$  constant at  $\frac{2V_{dc}}{3}$ . The first set is used for this paper. In the case of matrix converter, for all of the CCW and CW synchronously rotating vectors (both positive and negative end), one phase of input is connected to only one phase of output at any given time. Hence, assuming that the input voltages are balanced and only synchronously rotating vectors are used for converter control, the commonmode voltages defined in (3) for both positive and negative ends will always be zero. Hence, both differential  $(v_{\text{com,diff}})$ and average  $(v_{\text{com.sum}})$  common-mode voltages are held at zero.

It should be noted that all the space vectors mentioned above have a non-zero magnitude. To create a zero vector (which is required in output voltage control), the same space vector is applied to both positive and negative converters (such as  $\mathbf{U_1}$  and  $\mathbf{W_1}$ ) to get zero voltage across the load. This is further discussed in next section.

## III. GENERALIZED ANALYSIS FOR DUAL CONVERTER SPACE VECTORS

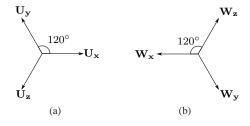

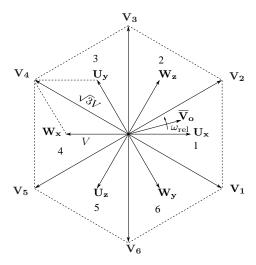

The space vectors for the positive end and the negative end converters (both dual two-level VSI and dual matrix converter) to generate zero common-mode voltage across the load are shown in Fig. 5(a) and Fig. 5(b) respectively. In Fig. 5, the space vectors  $\mathbf{U_x}$ ,  $\mathbf{W_x}$  and others can be related to the two-level inverter space vectors and matrix converter CCW and CW vectors using Table I. The vectors for the positive and the negative end converters can be combined to give six resultant vectors applied across the three phase load as shown in Fig. 6. For example, when space vectors  $\mathbf{U_x}$  and  $\mathbf{W_z}$  are simultaneously applied, the combined space vector  $\mathbf{V_2}$  is obtained.

The six resultant vectors  $V_1$  to  $V_6$  form six sectors labeled 1 to 6 and their magnitude is  $\sqrt{3}$  times the magnitude V

Fig. 5. (a) Generic positive end space vectors (b) Generic negative end space vectors

Fig. 6. Space vectors for dual converter

of individual converter space vectors. The magnitude V of the individual converter space vectors is  $V_{dc}$  in case of two-level vectors and  $\frac{3}{2}V_i$  in the case of CCW and CW vectors. These vectors, along with three zero vectors defined in (6), are used to synthesize the reference output voltage vector  $\overline{\mathbf{V}}_{\mathbf{o}}$  (bar indicates average over a switching cycle).

$$\begin{aligned} \mathbf{V_{zero,1}} &= \mathbf{U_x} + \mathbf{W_x} = 0 \\ \mathbf{V_{zero,2}} &= \mathbf{U_y} + \mathbf{W_y} = 0 \\ \mathbf{V_{zero,3}} &= \mathbf{U_z} + \mathbf{W_z} = 0 \end{aligned} \tag{6}$$

The instantaneous output voltage vector  $\mathbf{V_o}$  of the dual converter is formed by the sum of the positive end and negative end vectors  $\mathbf{U}$  and  $\mathbf{W}$ , as given in (7). It can be seen that this voltage vector is formed by the voltages across the load phases

$\label{table I} \textbf{TABLE I}$  Space vectors for CCW, CW and two-level case

| Generic                   | Two-level      | CCW          | CW           |

|---------------------------|----------------|--------------|--------------|

| vector                    | vector         | vector       | vector       |

| $\mathrm{U_x}$            | $U_1$          | $ m U_{abc}$ | $ m U_{acb}$ |

| $\mathbf{U}_{\mathbf{y}}$ | $U_3$          | $ m U_{cab}$ | $ m U_{bac}$ |

| $\mathbf{U}_{\mathbf{z}}$ | $\mathrm{U}_5$ | $ m U_{bca}$ | $ m U_{cba}$ |

| $\mathbf{W_x}$            | $\mathbf{W_1}$ | $W_{abc}$    | $ m W_{acb}$ |

| $\mathbf{W}_{\mathbf{y}}$ | $\mathbf{W_3}$ | $ m W_{cab}$ | $ m W_{bac}$ |

| $\mathbf{W}_{\mathbf{z}}$ | $\mathbf{W_5}$ | $W_{ m bca}$ | $ m W_{cba}$ |

i.e.  $v_{AA'}$ ,  $v_{BB'}$  and  $v_{CC'}$ .

$$\mathbf{V_o} = \mathbf{U} + \mathbf{W} = (v_{\text{AN}} + v_{\text{BN}}e^{j\frac{2\pi}{3}} + v_{\text{CN}}e^{-j\frac{2\pi}{3}}) + (-(v_{\text{A'N}} + v_{\text{B'N}}e^{j\frac{2\pi}{3}} + v_{\text{C'N}}e^{-j\frac{2\pi}{3}}))$$

$$= v_{\text{AA'}} + v_{\text{BB'}}e^{j\frac{2\pi}{3}} + v_{\text{CC'}}e^{-j\frac{2\pi}{3}}$$

(7)

Thus, the reference output voltages across the load phases will be defined between positive and negative end terminals, i.e.  $\overline{v}_{AA'} = V_o \cos(\omega_o t)$ ,  $\overline{v}_{BB'} = V_o \cos(\omega_o t - \frac{2\pi}{3})$  and  $\overline{v}_{CC'} = V_o \cos(\omega_o t + \frac{2\pi}{3})$ . The average output voltage vector  $\overline{\mathbf{V}}_{\mathbf{o}}$  (averaged over a switching period) is formed using these voltages. The voltage  $\overline{v}_{AA'}$  indicates the voltage across output phase AA' averaged over a single switching period. The voltages  $\overline{v}_{BB'}$  and  $\overline{v}_{CC'}$  indicate the same for output phases BB' and CC'.

The absolute speed of rotation of the reference output voltage vector is equal to the desired output frequency  $\omega_{\alpha}$ .

$$\overline{\mathbf{V}}_{\mathbf{o}} = \overline{v}_{AA'} + \overline{v}_{BB'} e^{j\frac{2\pi}{3}} + \overline{v}_{CC'} e^{-j\frac{2\pi}{3}} = \frac{3}{2} V_o e^{j\omega_o t}$$

(8)

In Fig. 6 however, the frequency  $\omega_{\rm rel}$  of  $V_{\rm o}$  is the relative frequency of  $V_{\rm o}$  with respect to the dual converter space vectors ( $V_{\rm 1}$ ,  $V_{\rm 2}$  etc.). This frequency is defined for the two-level, CCW and CW vectors in (9), (10) and (11) respectively. It can be seen that if input frequency  $\omega_i = 0$ , then the expression for  $\omega_{\rm rel}$  for two-level vectors in (9) is same as  $\omega_{\rm rel}$  for CCW and CW vectors in (10) and (11) respectively.

$$\omega_{\rm rel} = \omega_o$$

(for two-level vectors) (9)

$$\omega_{\rm rel} = \omega_o - \omega_i \quad \text{(for CCW vectors)}$$

(10)

$$\omega_{\rm rel} = \omega_o + \omega_i \quad \text{(for CW vectors)}$$

(11)

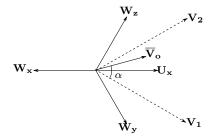

The output vector could be in one of the six sectors and the two space vectors bounding that sector are used to synthesize the output voltage vector on an average over a switching cycle. For example in Fig 6, the output voltage vector is in sector 1, so the space vectors  $V_1$  and  $V_2$  are to be used to synthesize it. Suppose, the duty ratios of  $\mathbf{V_1}$ ,  $\mathbf{V_2}$  and  $\mathbf{V_{zero,1}}$  are  $d_1$ ,  $d_2$  and  $d_{zero} = 1 - (d_1 + d_2)$  respectively. Then the output voltage vector is synthesized as in (12).

$$d_1\mathbf{V_1} + d_2\mathbf{V_2} + (1 - d_1 - d_2)\mathbf{V_{zero,1}} = \overline{\mathbf{V}_o}$$

(12)

From (6), (12) and Fig. 6, (13) is obtained.

$$\mathbf{U_x} + d_1 \mathbf{W_y} + d_2 \mathbf{W_z} + (1 - d_1 - d_2) \mathbf{W_x} = \overline{\mathbf{V_o}}$$

(13)

From (13), it is observed that the positive end converter vector  $\mathbf{U}_{\mathbf{x}}$  is ON for the entire switching period. The negative end converter vectors  $\mathbf{W}_{\mathbf{y}}$  and  $\mathbf{W}_{\mathbf{z}}$  are ON with duty ratios  $d_1$  and  $d_2$  respectively, while the vector  $\mathbf{W}_{\mathbf{x}}$  is ON for the remaining period, i.e. with a duty ratio of  $d_{zero}$  in a switching cycle.

It should be noted that in case of dual VSI, the proposed PWM scheme uses only one set of vectors out of  $U_1$ ,  $U_3$ ,  $U_5$ ,  $W_1$ ,  $W_3$ ,  $W_5$  and  $U_2$ ,  $U_4$ ,  $U_6$ ,  $W_2$ ,  $W_4$ ,  $W_6$ . This will lead to an imbalance in conduction losses, since the lower IGBTs (connected to negative terminal N of dc bus) in positive and negative end VSI will have twice the conduction period of upper IGBTs. This can be mitigated by using the two sets

Fig. 7.  $\overline{\mathbf{V}}_{\mathbf{o}}$  in Sector 1

in alternate output fundamental frequency periods. This will cause the common-mode voltages at positive and negative end to fluctuate between  $\frac{V_{dc}}{3}$  and  $\frac{2V_{dc}}{3}$ , but at a frequency closer to output frequency rather than at the switching frequency and shouldn't have effect on ground currents mitigation.

The switching losses however will be fairly balanced, because during three sectors, the positive end converter is clamped (both in case of dual MC and dual VSI). The positive end converter is switching during the rest three sectors and by applying the gate pulses such that each leg (in case of dual VSI) or each bidirectional switch (in case of dual MC) switches four times, thus equalizing number of switching transitions in all legs (dual VSI) or bidirectional switches (dual MC). The negative end converter also has the same number of switching transitions. Thus, a dual VSI will have total of four transitions per leg. A single VSI using conventional SVPWM (using all eight vectors) has only two transitions per leg in a switching period in all sectors. Thus, the dual VSI has twice the number of transitions compared to a single VSI. But as the voltage transfer ratio for dual converter is  $\sqrt{3}$  times that of a single VSI we can operate dual VSI at  $\frac{1}{\sqrt{3}}$  times the DC bus of the single VSI to achieve same maximum output voltage. Hence, switching losses will increase by  $\frac{2}{\sqrt{3}}$  times for the dual converter.

#### IV. DERIVATION OF CARRIER BASED ALGORITHM

The duty ratios  $d_1$  and  $d_2$  will now be derived in terms of the reference output phase voltages and input phase voltages. Suppose the output voltage vector is in sector 1, as shown in Fig.7.

For the CCW vectors, Table I and (13) give (14).

$$\mathbf{U_{abc}} + d_1 \mathbf{W_{cab}} + d_2 \mathbf{W_{bca}} + (1 - d_1 - d_2) \mathbf{W_{abc}} = \overline{\mathbf{V_o}}$$

(14)

Using (1), (2), (8), (14) and imposing that

$$\overline{v}_{AA'} + \overline{v}_{BB'} + \overline{v}_{CC'} = 0$$

the duty ratios  $d_1$  and  $d_2$  can be derived in terms of input voltages and average output voltages as in (15).

$$d_{1} = \frac{3\overline{v}_{\text{AA}'}v_{\text{cN}} + (\overline{v}_{\text{BB'}} - \overline{v}_{\text{CC'}})v_{\text{ab}}}{3(v_{\text{bN}}v_{\text{ab}} - v_{\text{cN}}v_{\text{ca}})}$$

$$d_{2} = \frac{3\overline{v}_{\text{AA}'}v_{\text{bN}} + (\overline{v}_{\text{BB'}} - \overline{v}_{\text{CC'}})v_{\text{ca}}}{3(v_{\text{bN}}v_{\text{ab}} - v_{\text{cN}}v_{\text{ca}})}$$

(15)

The quantity in the denominator is a constant and simplifies to  $-\frac{3\times3}{2}V_i^2$ . Also,  $v_{\rm aN}=V_i\cos(\omega_i t)$  and  $\overline{v}_{\rm AA'}=V_o\cos(\omega_o t)$

and so on. Using these expressions in (15) yields (16).

$$d_1 = -\frac{V_o \cos((\omega_o - \omega_i)t - \frac{2\pi}{3})}{\frac{3}{2}V_i}$$

$$d_2 = -\frac{V_o \cos((\omega_o - \omega_i)t + \frac{2\pi}{3})}{\frac{3}{2}V_i}$$

(16)

After repeating the preceding computations for all six sectors for CCW and CW vectors and using the analysis done in [38] for two-level inverter vectors, Table II is obtained,

| Sector | $d_1$  | $d_2$  |

|--------|--------|--------|

| 1      | $-m_y$ | $-m_z$ |

| 2      | $m_x$  | $m_y$  |

| 3      | $-m_z$ | $-m_x$ |

| 4      | $m_y$  | $m_z$  |

| 5      | $-m_x$ | $-m_y$ |

| 6      | $m_z$  | $m_x$  |

|        |        |        |

where for CCW vectors, the phase modulation indexes (MIs)  $m_x$ ,  $m_y$  and  $m_z$  are given by (17).

$$m_{x} = \frac{3\overline{v}_{\text{AA'}}v_{\text{aN}} + (\overline{v}_{\text{BB'}} - \overline{v}_{\text{CC'}})v_{\text{bc}}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} - \omega_{i})t)}{\frac{3}{2}V_{i}}$$

$$m_{y} = \frac{3\overline{v}_{\text{AA'}}v_{\text{cN}} + (\overline{v}_{\text{BB'}} - \overline{v}_{\text{CC'}})v_{\text{ab}}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} - \omega_{i})t - \frac{2\pi}{3})}{\frac{3}{2}V_{i}}$$

$$m_{z} = \frac{3\overline{v}_{\text{AA'}}v_{\text{bN}} + (\overline{v}_{\text{BB'}} - \overline{v}_{\text{CC'}})v_{\text{ca}}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} - \omega_{i})t + \frac{2\pi}{3})}{\frac{3}{2}V_{i}}$$

For CW vectors, the MIs  $m_x$ ,  $m_y$  and  $m_z$  are given by (18).

$$m_{x} = \frac{3\overline{v}_{AA'}v_{aN} - (\overline{v}_{BB'} - \overline{v}_{CC'})v_{bc}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} + \omega_{i})t)}{\frac{3}{2}V_{i}}$$

$$m_{y} = \frac{3\overline{v}_{AA'}v_{bN} - (\overline{v}_{BB'} - \overline{v}_{CC'})v_{ca}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} + \omega_{i})t - \frac{2\pi}{3})}{\frac{3}{2}V_{i}}$$

$$m_{z} = \frac{3\overline{v}_{AA'}v_{cN} - (\overline{v}_{BB'} - \overline{v}_{CC'})v_{ab}}{\frac{9}{2}V_{i}^{2}} = \frac{V_{o}\cos((\omega_{o} + \omega_{i})t + \frac{2\pi}{3})}{\frac{3}{2}V_{i}}$$

$$(18)$$

For dual two-level inverter, the MIs  $m_x$ ,  $m_y$  and  $m_z$  are given by (19).

$$m_x = \frac{\overline{v}_{AA'}}{V_{dc}} = \frac{V_o \cos(\omega_o t)}{V_{dc}}$$

$$m_y = \frac{\overline{v}_{BB'}}{V_{dc}} = \frac{V_o \cos(\omega_o t - \frac{2\pi}{3})}{V_{dc}}$$

$$m_z = \frac{\overline{v}_{CC'}}{V_{dc}} = \frac{V_o \cos(\omega_o t + \frac{2\pi}{3})}{V_{dc}}$$

(19)

Hence, in every sector, the duty ratios are a function of the phase modulation indexes (MIs)  $m_x$ ,  $m_y$  and  $m_z$ .

For the dual two-level inverter, the MIs are equal to reference phase voltages  $(\overline{v}_{AA'}, \overline{v}_{BB'}, \overline{v}_{CC'})$  divided by the dc bus voltage  $(V_{dc})$ . The frequency of these MIs is equal to output

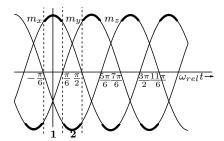

Fig. 8. Modulation indexes' waveforms

frequency  $\omega_o$  which is also equal to the relative frequency for two-level case defined in (9).

For the dual matrix converter, the amplitude of these modulation indexes is the ratio of peak phase output voltage  $V_o$  and 1.5 times of input peak phase voltage  $V_i$ . The frequency of the three CCW MIs in (17) is equal to relative frequency  $\omega_{\rm rel}$  defined in (10). Similarly, the frequency for the CW MIs in (18) is the relative frequency defined in (11).

With these observations a common algorithm can be used to find the duty ratios for different phases for both dual matrix converter and dual two-level inverter. Fig. 8 shows the three phase modulation indexes against time.

In the figure, the maximum and the minimum modulation indexes are highlighted in alternate sectors e.g. sector 1 and sector 2 (both bounded by vertical dotted lines) have the maximum MI and the minimum MI highlighted respectively. Following observations are made.

- In sector 1, the absolute value of phase modulation index  $m_x$  i.e.  $|m_x|$  is maximum among absolute values  $|m_x|$ ,  $|m_y|$  and  $|m_z|$ . In sector 1, the phase modulation index  $m_x$  is termed as the absolute maximum MI and the other two MIs  $(m_y)$  and  $m_z$  are termed non-maximum MIs.

- Throughout the sector 1, the positive end converter is clamped and always applies one space vector i.e.  $\mathbf{U_x}$  and the modulation index  $m_x$  is absolute maximum and positive, as seen in Fig. 8. In other sectors as well, the sign of the MI which is absolute maximum decides which converter is clamped (positive for positive end converter and negative for negative end converter). The space vector applied by the clamped converter is corresponding to MI which is absolute maximum., i.e.  $\mathbf{U_x}$  in sector 1 and so on.

- In sector 1, for the negative end converter, the duty ratios for space vectors corresponding to non-maximum MIs  $(m_y, m_z)$  i.e.  $\mathbf{W_y}$  and  $\mathbf{W_z}$  are equal to  $d_1$  and  $d_2$  respectively. As seen from Table II,  $d_1 = -m_y$  and  $d_2 = -m_z$ , i.e. the negative of non-maximum MIs. In Fig. 8, the non-maximum MIs  $m_y$  and  $m_z$  are negative in sector 1. Hence,  $d_1 = |m_y|$  and  $d_2 = |m_z|$ . Thus,  $\mathbf{W_y}$  and  $\mathbf{W_z}$  are applied with duty ratios equal to absolute value of corresponding MIs.

- In sector 1, the duty ratio of the negative end converter for space vector corresponding to absolute maximum MI  $(m_x)$  i.e.  $\mathbf{W_x}$  is equal to  $1-(d_1+d_2)=1+(m_y+m_z)$  i.e.  $1-m_x$ . This can be rewritten as  $1-|m_x|$  since  $m_x$  is positive in sector 1 as seen in Fig. 8.

TABLE III

DUTY RATIOS IN TERMS OF MODULATION INDEXES

| Duty                          | MI with maximum absolute value is positive |               | MI with maximum absolute value is negative |           |               |               |

|-------------------------------|--------------------------------------------|---------------|--------------------------------------------|-----------|---------------|---------------|

| ratio                         | $m_x$                                      | $m_y$         | $m_z$                                      | $m_x$     | $m_y$         | $m_z$         |

| $d_{\mathbf{U_x}}$            | 1                                          | 0             | 0                                          | $1- m_x $ | $ m_x $       | $ m_x $       |

| $d_{\mathbf{U_y}}$            | 0                                          | 1             | 0                                          | $ m_y $   | $1$ - $ m_y $ | $ m_y $       |

| $d_{\mathbf{U_z}}$            | 0                                          | 0             | 1                                          | $ m_z $   | $ m_z $       | $1$ - $ m_z $ |

| $d_{\mathbf{W}_{\mathbf{x}}}$ | $1- m_x $                                  | $ m_x $       | $ m_x $                                    | 1         | 0             | 0             |

| $d_{\mathbf{W_y}}$            | $ m_y $                                    | $1$ - $ m_y $ | $ m_y $                                    | 0         | 1             | 0             |

| $d_{\mathbf{W}_{\mathbf{z}}}$ | $ m_z $                                    | $ m_z $       | $1$ - $ m_z $                              | 0         | 0             | 1             |

Total computations: 6 multiplications, 8 additions/subtractions 8 comparisons, 1 shift operation

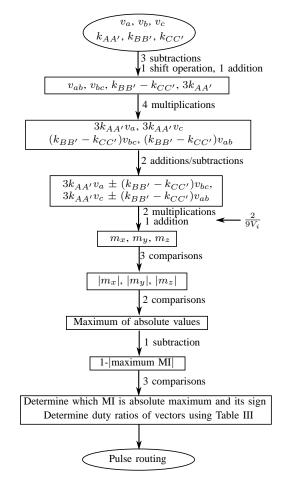

Fig. 9. Carrier based implementation of matrix converter PWM using CCW and CW vectors

Similar analysis can be done for other sectors to derive the duty ratios for all the vectors. The information for all sectors is summarized in Table III, which gives the duty ratios for all space vectors in terms of MIs  $m_x$ ,  $m_y$  and  $m_z$ .

In the table, the duty ratio of space vector  $\mathbf{U_x}$  is denoted by  $d_{\mathbf{U_x}}$  and so on.  $\mathbf{U_x}$ ,  $\mathbf{U_y}$  and other space vectors can be identified using Table I for CCW, CW and two-level inverter vectors. Note that the MIs  $m_x$ ,  $m_y$  and  $m_z$  have been defined in (17), (18) and (19) for CCW, CW and two-level inverter cases respectively. A flow chart for calculating duty ratios

using carrier based algorithm for open-end winding matrix converter drive is given in Fig. 9. As a preliminary step, the CCW and CW modulation indexes defined in (17) and (18) respectively are rewritten as shown in (20) and (21) respectively.

$$m_{x} = \frac{3\overline{v}_{AA'}v_{aN} + (\overline{v}_{BB'} - \overline{v}_{CC'})v_{bc}}{\frac{9}{2}V_{i}^{2}}$$

$$= [3k_{AA'}v_{aN} + (k_{BB'} - k_{CC'})v_{bc}] \left(\frac{2}{9V_{i}}\right)$$

$$m_{y} = \frac{3\overline{v}_{AA'}v_{cN} + (\overline{v}_{BB'} - \overline{v}_{CC'})v_{ab}}{\frac{9}{2}V_{i}^{2}}$$

$$= [3k_{AA'}v_{cN} + (k_{BB'} - k_{CC'})V_{ab}] \left(\frac{2}{9V_{i}}\right)$$

$$m_{z} = -(m_{x} + m_{y})$$

$$(20)$$

$$m_{x} = \frac{3\overline{v}_{AA'}v_{aN} - (\overline{v}_{BB'} - \overline{v}_{CC'})v_{bc}}{\frac{9}{2}V_{i}^{2}}$$

$$= [3k_{AA'}v_{aN} - (k_{BB'} - k_{CC'})v_{bc}] \left(\frac{2}{9V_{i}}\right)$$

$$m_{z} = \frac{3\overline{v}_{AA'}v_{cN} - (\overline{v}_{BB'} - \overline{v}_{CC'})v_{ab}}{\frac{9}{2}V_{i}^{2}}$$

$$= [3k_{AA'}v_{cN} - (k_{BB'} - k_{CC'})V_{ab}] \left(\frac{2}{9V_{i}}\right)$$

$$m_{y} = -(m_{x} + m_{z})$$

$$(21)$$

where

$$k_{\text{II}'} = \frac{\overline{v}_{\text{II}'}}{V_i}$$

I = A, B, C (22)

Thus, the expression  $[3k_{\mathrm{AA'}}v_a \pm (k_{\mathrm{BB'}} - k_{\mathrm{CC'}})v_{\mathrm{bc}}]\left(\frac{2}{9V_i}\right)$  equals CCW MI  $m_x$  when + sign is used in place of  $\pm$  and equals CW MI  $m_x$  when - sign is used in place of  $\pm$ . Also, expression  $[3k_{\mathrm{AA'}}v_c \pm (k_{\mathrm{BB'}} - k_{\mathrm{CC'}})V_{ab}]\left(\frac{2}{9v_i}\right)$  equals CCW MI  $m_y$  when + sign is used in place of  $\pm$  and equals the CW MI  $m_z$  when - sign is used in place of  $\pm$ .

It is assumed that  $k_{AA'}$ ,  $k_{BB'}$  and  $k_{CC'}$  defined in (22), the input voltages  $v_{\rm aN}$ ,  $v_{\rm bN}$  and  $v_{\rm cN}$  and the quantity  $\frac{2}{9V_i}$  are given at the beginning of the algorithm. The flowchart in Fig. 9 is explained as follows:

- 1) Compute  $3k_{AA'}$  [1 addition, 1 shift operation],  $v_{\rm ab}$  [1 subtraction],  $v_{\rm bc}$  [1 subtraction] and  $k_{\rm BB'}-k_{\rm CC'}$  [1 subtraction]. [Total: 3 subtractions, 1 addition, 1 shift operation]

- 2) Compute  $3k_{\rm AA'}v_{\rm aN}$ ,  $3k_{\rm AA'}v_{\rm cN}$ ,  $(k_{\rm BB'}-k_{\rm CC'})v_{\rm bc}$  and  $(k_{\rm BB'}-k_{\rm CC'})v_{\rm ab}$ , using quantities computed in the previous step. [Total: 4 multiplications]

- 3) Compute  $3k_{\rm AA'}v_{\rm aN} \pm (k_{\rm BB'} k_{\rm CC'})v_{\rm bc}$  [1 addition/subtraction] and  $3k_{\rm AA'}v_{\rm cN} \pm (k_{\rm BB'} k_{\rm CC'})v_{\rm ab}$  [1 addition/subtraction]. The plus sign  $\pm$  is for CCW vectors and the minus sign is for CW vectors. [Total: 2 subtractions/additions]

- 4) Compute  $(3k_{\rm AA'}v_{\rm aN} \pm (k_{\rm BB'} k_{\rm CC'})v_{\rm bc})\frac{2}{9V_i}$  [1 multiplication] and  $(3k_{\rm AA'}v_{\rm cN} \pm (k_{\rm BB'} k_{\rm CC'})v_{\rm ab})\frac{2}{9v_i}$  [1 multiplication]. This gives CCW MIs  $m_x$  and  $m_y$  or

Fig. 10. Duty ratio waveforms for all positive and negative end space vectors (and switches)

CW MIs  $m_x$  and  $m_z$  as explained in (20) and (21). Calculate  $m_z = -(m_x + m_y)$  for CCW vectors or  $m_y = -(m_x + m_z)$  for CW vectors [1 addition]. Now all the MIs required for duty ratio computation are obtained. [Total: 2 multiplications, 1 addition]

- 5) Find  $|m_x|$ ,  $|m_y|$  and  $|m_z|$ . [Total: 3 comparisons]

- 6) Compare  $|m_x|$ ,  $|m_y|$  and  $|m_z|$  to identify maximum of these three. [Total: 2 *comparisons*]

- 7) Find 1-|Maximum MI|. [Total: 1 subtraction]

- 8) Determine which is the MI whose absolute value is maximum by comparing  $|m_x|$ ,  $|m_y|$  and  $|m_z|$  with the absolute maximum MI found in step 6 [2 comparisons]. Then, find the sign of this absolute maximum MI [1 comparison]. [Total: 3 comparisons]

- Use the Table III to get the duty ratio of individual vectors and hence the individual switches using Table I.

As seen from above explanation, the carrier based algorithm requires a total of 6 multiplications, 8 additions/subtractions, 8 comparisons and 1 shift operation. These computations have also been shown denoted in Fig. 9.

As an example , let  $|m_y|$  be maximum and  $m_y$  be positive. Then using Table III, the positive end converter is clamped to space vector  $\mathbf{U_y}$ . The duty ratios of negative end converter's vectors  $\mathbf{W_x}$ ,  $\mathbf{W_y}$  and  $\mathbf{W_z}$  are  $|m_x|$ ,  $1-|m_y|$  and  $m_z$  respectively. If the CCW vectors are being used, then using Table I, the positive end matrix converter is clamped to  $\mathbf{U_{cab}}$ . The duty ratios of space vectors  $\mathbf{W_{abc}}$ ,  $\mathbf{W_{cab}}$  and  $\mathbf{W_{bca}}$  are  $|m_x|$ ,  $1-|m_y|$  and  $m_z$  respectively.

It should be noted that despite using space vector equations to arrive at the carrier based algorithm, the finalized carrier based algorithm mentioned above doesn't require any knowledge of space vectors.

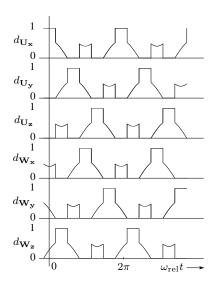

The duty ratio waveforms for the three positive end vectors and the three negative end vectors derived using the carrier based algorithm are shown in Fig. 10. In the figure,  $d_{\rm U_x}$  denotes the duty ratio waveform of positive end generalized

TABLE IV

DUTY RATIOS IN EACH SECTOR

| Duty Sector<br>Ratio          | 1          | 2          | 3          | 4          | 5          | 6          |

|-------------------------------|------------|------------|------------|------------|------------|------------|

| $d_{\mathbf{U_x}}$            | 1          | $d_1$      | 0          | $d_{zero}$ | 0          | $d_2$      |

| $d_{\mathbf{U_y}}$            | 0          | $d_2$      | 1          | $d_1$      | 0          | $d_{zero}$ |

| $d_{\mathbf{U}_{\mathbf{z}}}$ | 0          | $d_{zero}$ | 0          | $d_2$      | 1          | $d_1$      |

| $d_{\mathbf{W_x}}$            | $d_{zero}$ | 0          | $d_2$      | 1          | $d_1$      | 0          |

| $d_{\mathbf{W}_{\mathbf{y}}}$ | $d_1$      | 0          | $d_{zero}$ | 0          | $d_2$      | 1          |

| $d\mathbf{w}_{\mathbf{z}}$    | $d_2$      | 1          | $d_1$      | 0          | $d_{zero}$ | 0          |

vector  $\mathbf{U_x}$ . The other waveforms similarly denote the duty ratios of corresponding generalized vectors. The six waveforms are identical in shape and size but are displaced in time. The waveforms  $d_{\mathbf{U_y}}$  and  $d_{\mathbf{U_z}}$  lag  $d_{\mathbf{U_x}}$  by  $120^\circ$  and  $240^\circ$  respectively. The negative end vector duty ratio waveform  $d_{\mathbf{W_x}}$  is displaced by  $180^\circ$  wrt to corresponding positive end vector duty ratio waveform  $d_{\mathbf{U_x}}$ . The negative end vector duty ratio waveforms are also displaced by  $120^\circ$  wrt to each other. It should be noted that the frequency of all these duty ratio waveforms is the relative frequency  $\omega_{\rm rel}$ .

The waveforms in Fig. 10 are duty ratio signals for space vectors. However, in any of the three sets (two-level, CCW, CW), one leg (in case of dual two-level VSI) or one bidirectional switch (in case of dual matrix converter) is related to only one space vector. As an example (using  $U_1$ ,  $U_3$  and U<sub>5</sub> for modulating positive end converter), in the dual twolevel VSI, the leg connected to output phase A is turned ON (or connected to dc bus terminal P) only when vector  $U_1$ is applied and is turned OFF (connected to dc bus terminal N) when any other two vectors  $(U_3, U_5)$  are applied. Thus, in Fig. 10, the waveform  $d_{\mathbf{U}_{\mathbf{x}}}$  corresponds to the duty ratio waveform of  $U_1$  (using Table I) with  $\omega_{\rm rel} = \omega_o$  and hence is the duty ratio waveform for the inverter leg connected to output phase A. In the matrix converter case, when using CCW vectors, the switches aA, bB and cC are turned ON only when the CCW vector  $U_{abc}$  is applied and are OFF when any other CCW vector is applied. In Fig. 10, the waveform d<sub>U</sub>, corresponds to the duty ratio waveform of Uabc (using table I) with  $\omega_{\rm rel} = \omega_o - \omega_i$ . Hence, this is the duty ratio waveform for switches aA, bB and cC when using CCW vectors. A similar explanation is applicable for CW vectors.

It must be noted, in case of simple carrier based operation of a VSI, modulation/duty ratio signals can be directly compared with a carrier to generate gating waveforms. In this case an additional simple combinatorial operation with the generated pulses is necessary to avoid over lapping of two active pulses in time. For example in a carrier/sampling cycle the pulses for aA  $(U_{abc})$  and cA  $(U_{cab})$  must not overlap in time.

#### V. COMPARISON BETWEEN CARRIER BASED AND SPACE VECTOR APPROACHES FOR PWM OF DUAL MATRIX AND TWO-LEVEL VSI

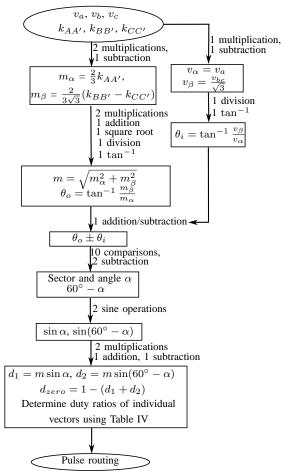

An algorithm for the space vector based approach for PWM of open-end winding matrix converter drive using both CCW

Total computations: 1 square root, 2 divisions, 7 multiplications, 2 tan<sup>-1</sup>, 2 sine, 8 additions/subtractions, 10 comparisons

Fig. 11. Space vector based PWM of dual matrix converter using CCW and CW vectors

and CW vectors is shown in Fig. 11. It is assumed that  $k_{AA'}$ ,  $k_{BB'}$  and  $k_{CC'}$  defined in (22), the input voltages  $v_a$ ,  $v_b$  and  $v_c$  are given at the starting of the computation.

The flowchart for space vector based approach in Fig. 11 is explained below:

- 1) The input phase voltages  $v_{\rm aN}$ ,  $v_{\rm bN}$  and  $v_{\rm cN}$  are converted to  $\alpha\beta$  axis, using  $v_{\alpha}=v_{\rm aN}$  and  $v_{\beta}=\frac{v_{\rm bc}}{\sqrt{3}}$  [I subtraction, I multiplication]. Input voltage phase  $\theta_i$  is calculated as  $\tan^{-1}\frac{v_{\beta}}{v_{\alpha}}$  [I division, I  $\tan^{-1}$ ]. [Total: I multiplication, I subtraction, I division, I  $\tan^{-1}$ ]

- 2)  $m_{\alpha} = \frac{2}{3}k_{AA'}$  [1 multiplication] and  $m_{\beta} = \frac{2}{3\sqrt{3}}(k_{BB'} k_{CC'})$  [1 subtraction, 1 multiplication] are calculated. [Total: 1 subtraction, 2 multiplications]

- 3) The output modulation index  $m = \sqrt{m_{\alpha}^2 + m_{\beta}^2}$  is computed [2 multiplications (for computing  $m_{\alpha}^2$  and  $m_{\beta}^2$ ), 1 addition, 1 square root]. Output voltage angle is computed using  $\theta_o = \tan^{-1} \frac{m_{\beta}}{m_{\alpha}}$  [1 division, 1  $\tan^{-1}$ ]. [Total: 2 multiplications, 1 addition, 1 square root operation, 1 division, 1  $\tan^{-1}$ ]

- 4)  $\theta_i \pm \theta_o$  is computed (either added for CW vectors or subtracted for CCW vectors). [1 subtraction/addition]

- 5) To determine the sector,  $\theta_o \pm \theta_i$  is compared with the

TABLE V

COMPUTATIONS REQUIRED FOR CARRIER BASED AND SPACE VECTOR

BASED APPROACHES FOR PWM OF DUAL MATRIX CONVERTER

| Computation          | Carrier based | Space vector based |

|----------------------|---------------|--------------------|

|                      | approach      | approach           |

| Comparison           | 8             | 10                 |

| Shift operation      | 1             | 0                  |

| Addition/Subtraction | 8             | 8                  |

| Multiplication       | 6             | 7                  |

| Division             | 0             | 2                  |

| Sine                 | 0             | 2                  |

| $\tan^{-1}$          | 0             | 2                  |

| Square root          | 0             | 1                  |

upper and lower angular bounds of each sector [10 comparisons in worst case]. Then, angle  $\alpha$  is determined by subtracting appropriate multiple of  $\frac{\pi}{3}$  from  $\theta_o$  [1 subtraction]. Then  $(60^{\circ}-\alpha)$  is computed [1 subtraction]. [Total: 10 comparisons, 2 subtractions]

- 6) Compute  $\sin \alpha$  and  $\sin (60^{\circ} \alpha)$ . [2  $\sin$  operations]

- 7) Compute duty ratios  $d_1 = m \sin(\alpha)$  and  $d_2 = m \sin(60^{\circ} \alpha)$  [2 multiplications]. Calculate  $d_{zero} = 1 (d_1 + d_2)$  [ 1 addition, 1 subtraction]. [Total: 2 multiplications, 1 addition, 1 subtraction]

- 8) With sector,  $d_1$ ,  $d_2$  and  $d_{zero}$  known, Table IV and Table I are used to determine which space vector is applied with what duty ratio. This part is common with the carrier based algorithm and takes the same computations (a case or if else statement). Hence, it is not be considered in the comparison.

Based on above discussion, the total computations needed for the space vector based implementation of PWM for dual matrix converter using CCW and CW vectors are 1 square root, 2 tan<sup>-1</sup>, 2 sin, 2 divisions, 7 multiplications, 8 additions/subtractions, 10 comparisons. The flowchart in Fig. 9 for carrier based approach for dual matrix converter PWM using CCW or CW vectors is explained in Section IV and the various calculations required for the steps have been explained before as well as shown in the flowchart.

It is observed from the above discussion and the flowcharts that the carrier based approach takes fewer computations than the space vector approach for the PWM control of dual matrix converter. The computations required are summarized seen in Table V.

The Verilog code for both the methods was developed and implemented using Xilinx ISE Editor to check the resources. The FPGA used was Xilinx Spartan 3 XC3S500E. The resource requirements of both techniques is given in Table VI, which shows that the resource requirements are much more in space vector based approach. The CORDIC IP core from Xilinx was used to do the square root and all trigonometric operations needed by the space vector approach.

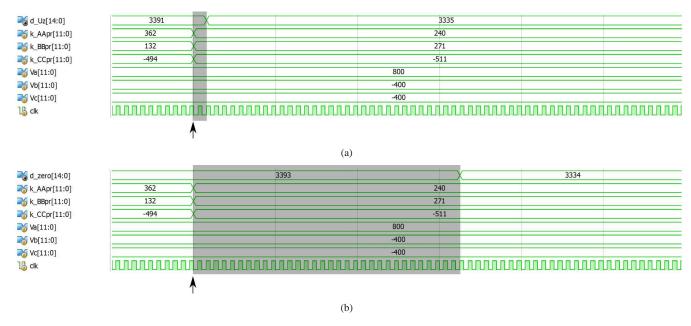

The latencies of Verilog code for carrier based and space vector based approaches for open-end winding matrix converter drive are shown in Fig. 12(a) and Fig. 12(b) respectively. In Fig. 12(a), the inputs  $k_{AA'}$ ,  $k_{BB'}$  and  $k_{CC'}$  (denoted k\_AApr, k\_BBpr and k\_CCpr respectively in the figure)

TABLE VI

RESOURCE REQUIREMENTS OF CARRIER BASED AND SPACE VECTOR

BASED APPROACHES FOR PWM OF DUAL MATRIX CONVERTER

| Resource used                           | Carrier based approach | Space vector approach    |  |

|-----------------------------------------|------------------------|--------------------------|--|

| No. of slice flip-flops                 | 71 (1%)                | 2436 (26%)               |  |

| No. of 4 input LUTs No. of Logic slices | 461 (4%)<br>271 (5%)   | 2670 (28%)<br>1590 (34%) |  |

| No. of MULT18X18SIOs                    | 6 (30%)                | 7 (35%)                  |  |

TABLE VII

SIMULATION AND EXPERIMENTAL PARAMETERS FOR DUAL TWO-LEVEL INVERTER AND DUAL MATRIX CONVERTER OPEN-END WINDING DRIVES

| Parameter                      | Dual two<br>level inverter | Dual matrix converter            |  |

|--------------------------------|----------------------------|----------------------------------|--|

| DC bus voltage                 | 100 V                      | N/A                              |  |

| Input voltage (line-line rms)  | N/A                        | 69.2 V                           |  |

| Input frequency                | N/A                        | 60 Hz                            |  |

| Output voltage (line-line rms) | 87 V                       | 69.2 V                           |  |

| Output frequency               | 60 Hz                      | 28 Hz                            |  |

| Switching frequency            | 5 kHz                      | 5 kHz                            |  |

| Load                           | 31.0∠39.0° Ω               | $15.4\angle 36.0^{\circ} \Omega$ |  |

change at the beginning of the shaded region (marked by an arrow). The output  $d_{\mathbf{U_z}}$  i.e., the duty ratio of vector  $\mathbf{U_z}$  (top signal denoted as  $d_{\mathbf{U}}\mathbf{Z}$  in the figure) changes after two clock cycles (shown in the shaded area). In Fig. 12(b), the inputs  $k_{AA'}$ ,  $k_{BB'}$  and  $k_{CC'}$  (denoted  $k_{\mathbf{A}}\mathbf{A}$  or  $k_{\mathbf{B}}\mathbf{B}$  pr and  $k_{\mathbf{C}}\mathbf{C}$  respectively in the figure) change at the beginning of the shaded region. The output  $d_{zero}$  i.e., the duty ratio of the zero vector (top signal denoted as dz in the figure) in the current sector changes after thirty three clock cycles (shown in the shaded area). Thus, latency of the carrier based algorithm as seen in Fig. 9 is two clock cycles. The latency of the space vector based approach as seen in Fig. 11 has a latency of thirty three clock cycles, which is much more than that of carrier based approach.

The carrier based and space vector based approaches for PWM of open-end winding two-level inverter drive are special cases of corresponding approaches for PWM of open-end winding matrix converter drive. So, the carrier based and space vector based approaches for PWM of two-level inverter compare similarly.

#### VI. SIMULATION RESULTS

The parameters used for the simulation of dual two-level inverter drive using carrier based PWM are given in second column of Table VII.

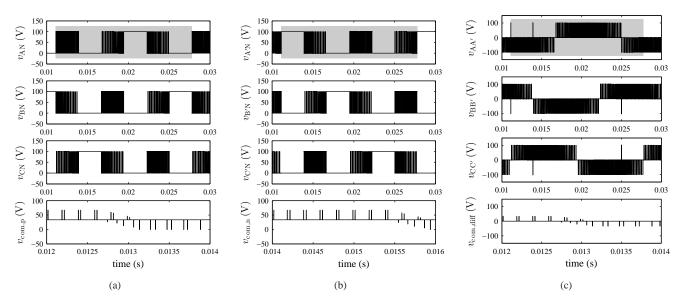

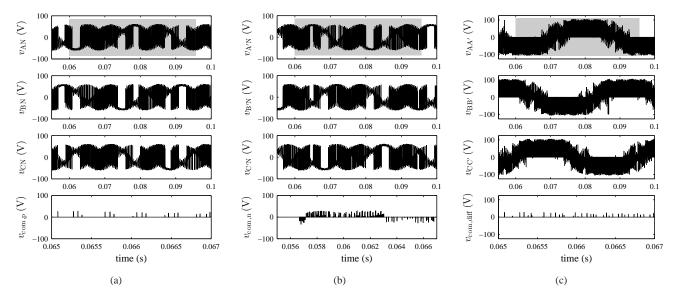

The simulation results for dual two-level inverter are shown in Fig. 13, Fig. 14 and Fig. 15. The positive end and negative end pole voltages and common-mode voltage are shown in Fig. 13(a) and Fig. 13(b) respectively. The voltages across output phases and differential common-mode voltage is shown in Fig. 13(c). Dead times and device drops have been included in the simulations to remain close to experimental conditions. It is observed that barring the small glitches due to device drops

Fig. 12. Latency in Verilog code for PWM of dual matrix converter (a) Carrier based approach (b) Space vector based approach

Fig. 13. Simulation results for Dual two-level inverter (gray patch in top graphs indicates the length of one cycle of output fundamental frequency) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) (b)Negative end pole voltages (top three graphs) and CMV (bottom graph) (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load

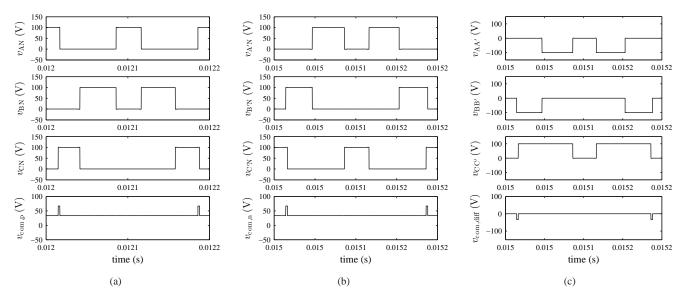

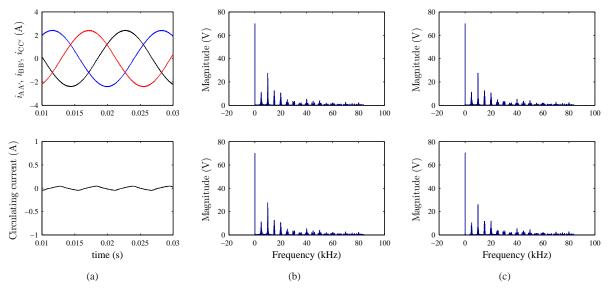

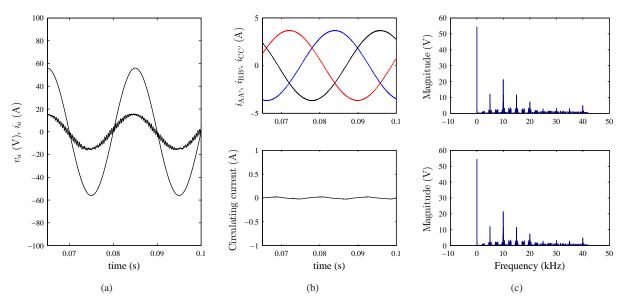

and dead times [40], the positive and negative end common-mode voltages are held flat at 33.33 V, which is equal to  $\frac{1}{3}$ rd of the dc bus voltage  $V_{dc}$ . Thus their average sum and difference should also have constant values (ignoring non-idealities), which should help in mitigating the problems of circulating currents and EMI. In all these figures, a gray patch has been drawn in the top graph to denote one cycle of the output fundamental frequency  $\omega_o$ . In Fig. 14, the positive end and negative end pole voltages and voltage across output phases have been shown for one switching cycle for easier viewing. Fig. 15(a) displays the output currents and the circulating current. The output currents appear balanced and sinusoidal as desired, while the circulating current is much smaller than

the output currents. The Fourier spectra of voltage  $v_{\rm AA'}$  across output phase A are shown in Fig. 15(b) for carrier based and space vector based techniques respectively. The spectra are nearly identical, which implies that the carrier based method generates identical pulses to that of space vector approach.

Lastly, the Fourier spectra of voltage across load phase A are shown for dual VSI with CMV elimination and single VSI using conventional SVPWM (all eight vectors) in Fig. 15(c). It is seen that they are nearly identical, indicating that the differential mode power quality of dual VSI with CMV elimination is same as that of single VSI with conventional PWM.

The parameters used for simulation of dual matrix converter using carrier based PWM are given in third column of Table

Fig. 14. Simulation results (Zoomed voltages for Dual two-level inverter) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) (b)Negative end pole voltages (top three graphs) and CMV (bottom graph) (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load

Fig. 15. Simulation results (dual two-level inverter) (a) Three phase load currents (top graph) and circulating current (bottom graph) (b) Fourier spectrum of voltage  $v_{\rm AA'}$  across load phase A using carrier based method (top graph) and space vector method (bottom graph) (c) Fourier spectrum of voltage  $v_{\rm AA'}$  across phase A for dual VSI (top graph) and Fourier spectrum of output phase voltage  $v_{\rm An}$  in single VSI (bottom graph)

#### VII.

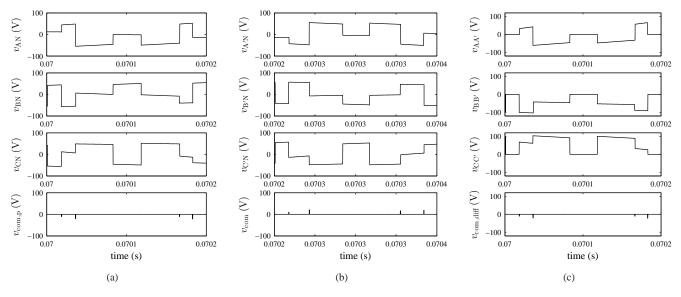

The simulation results for dual matrix converter are shown in Fig. 16, Fig. 17 and Fig. 18. The positive end and negative end pole voltages and common-mode voltage are shown in Fig. 16(a) and Fig. 16(b) respectively. The voltages across output phases and differential common-mode voltage is shown in Fig. 16(c). Commutation periods and device drops have been included in the simulations to remain close to experimental conditions. It is observed that excluding the small glitches due to commutation periods and device drops [40], the positive and negative end common-mode voltages are held flat at 0 V. Thus their average sum and difference should also be zero (ignoring non-idealities), which should help in mitigating the problems of circulating currents and EMI. In all these figures,

a gray patch has been drawn in the top graph to denote one cycle of the output fundamental frequency  $\omega_o$ . In Fig. 17, the positive end and negative end pole voltages and voltage across output phases have been shown for one switching cycle for easier viewing. In Fig. 18(a), the input voltage  $v_{\rm aN}$  and current (filtered and zoomed five times)  $i_{\rm a}$  are shown. It can be seen that they are nearly in phase, indicating unity power factor which is due to equal utilization of CCW and CW vectors [21]. Fig. 18(b) displays the output currents and the circulating current. The output currents appear balanced and sinusoidal as desired, while the circulating current is much smaller than the output currents. Finally, in Fig. 18(c), the Fourier spectra of voltage  $v_{\rm AA'}$  across output phase A are shown for carrier based

Fig. 16. Simulation results for Dual matrix converter (gray patch in top graphs indicates the length of one cycle of output fundamental frequency) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) (b)Negative end pole voltages (top three graphs) and CMV (bottom graph) (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load

Fig. 17. Simulation results (Zoomed voltages for Dual matrix converter) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) (b)Negative end pole voltages (top three graphs) and CMV (bottom graph) (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load

and space vector based techniques respectively. The spectra are nearly identical, which implies that the carrier based method generates identical pulses to that of space vector approach.

#### VII. EXPERIMENTAL RESULTS

The proposed PWM technique was tested on prototype hardware setups of dual two-level inverter and dual matrix converter open-end winding drives. In this section, a brief description of the hardware setups has been given along with key experimental results.

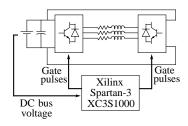

The dual two-level inverter was built using two Microsemi APTGF90TA60PG IGBT modules. The gate drivers used are Concept 6SD106EI. The proposed PWM technique was

implemented using a Digilent Spartan 3 Starter board with Xilinx XC3S1000 FPGA. A diagram of the circuit is given in Fig. 19. A dead band of 2  $\mu$ s is present between the pulses of upper and lower switch of any leg in the inverter. The experimental settings for two-level inverter setup are given in second column of Table VII.

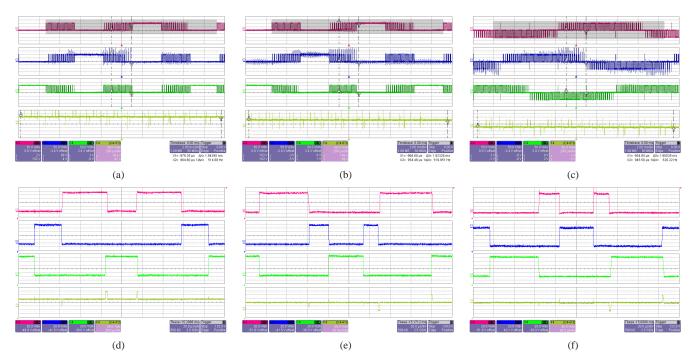

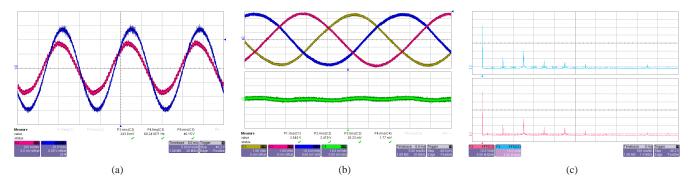

The experimental results for dual two-level inverter are given in Fig. 20 and Fig. 21. The positive end and negative end pole voltages and common-mode voltage are shown in Fig. 20(a) and Fig. 20(b). The voltages across output phases and the differential common-mode voltage are shown in Fig. 20(c). A gray patch in the top graphs of these three figures indicates one cycle of output fundamental frequency. It is observed that the positive end and negative end common-mode voltages are

Fig. 18. Simulation results (Dual matrix converter) (a) Input current (zoomed five times for viewing ease) and voltage of phase a (b) Three phase load currents (top graph) and circulating current (bottom graph) (c) Fourier spectrum of voltage  $v_{\rm AA'}$  across load phase A using carrier based method (top graph) and space vector method (bottom graph)

Fig. 19. Diagram of the experimental setup for dual two-level inverter

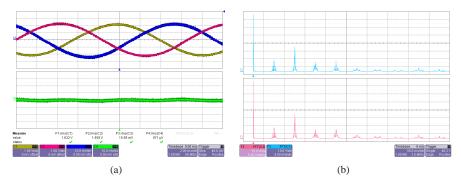

held at a constant value and the differential common-mode voltage is held at zero, barring the glitches due to dead times and device drops [40]. Zoomed versions of all these voltages are provided in Fig. 20(d)-20(f) for better viewing. The three phase load currents and circulating current are shown in Fig. 21(a). The currents appear as balanced and sinusoidal. The circulating is current non-zero, however much smaller than the load currents. Fourier spectra of the voltage  $v_{\rm AA'}$  are given for PWM of dual two-level inverter using carrier based and space vector based approaches in Fig. 21(b). It is seen that the spectra are nearly identical and devoid of low order harmonics.

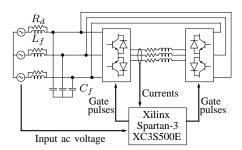

The dual matrix converter setup was built using six Microsemi APTGT75TDU120PG IGBT modules and the gate drivers used are Concept 2SD106AI. The proposed PWM technique was implemented on a Xilinx XC3S500E FPGA board. A diagram of the setup is shown in Fig. 22. Four step commutation was used with a total commutation period of 1.5  $\mu$ s. This requires sensing of the load currents. The experimental settings for dual matrix converter setup are given in rightmost column of Table VII.

The filter components used are  $R_d=12.5~\Omega,\, L_f=1.4~\mathrm{mH}$  and  $C_f=35~\mu\mathrm{F}.$

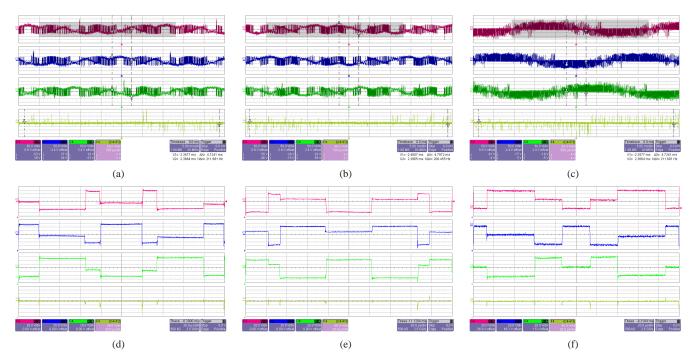

The experimental results for dual matrix converter are given in Fig. 23 and Fig. 24. The positive end and negative end

pole voltages and common-mode voltage are shown in Fig. 23(a) and Fig. 23(b). The voltages across output phases and the differential common-mode voltage are shown in Fig. 23(c). A gray patch in the top graphs of these three figures indicates one cycle of output fundamental frequency. It is observed that the positive end, negative end and the differential commonmode voltages are held at zero, barring the glitches due to commutation periods times and device drops [40]. Zoomed versions of all these voltages are provided in Fig. 23(d)-23(f) for better viewing. The input phase voltage  $v_{\rm aN}$  and phase current  $i_a$  are shown in Fig. 24(a). It can be seen that the input voltage and current (filtered) are nearly in phase (current leads slightly due to input filter), indicating unity power factor due to equal usage of CCW and CW vector [21]. The three phase load currents and circulating current are shown in Fig. 24(b). The currents appear as balanced and sinusoidal. The circulating current is non-zero, however much smaller than the load currents. Fourier spectra of the voltage  $v_{AA'}$  are given for PWM of dual matrix converter using carrier based and space vector based approaches in Fig. 24(c). It is seen that the spectra are nearly identical and devoid of low order harmonics.

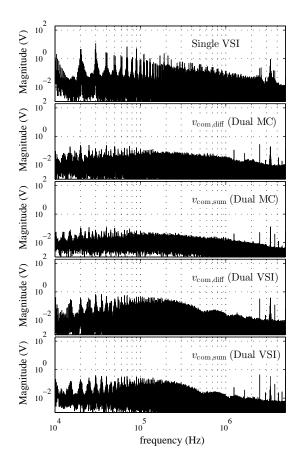

Finally, Fig. 25 shows the high frequency spectra of common-mode voltages generated by a single two-level VSI, a dual two-level VSI with common-mode voltage elimination and a dual matrix converter with common-mode voltage elimination. The single VSI and dual VSI were operated at 100 V dc bus voltage and the dual matrix converter was operated with a line-line peak voltage 97.86 V (rms 69.2 V) for this comparison. It can be seen that the high frequency common-mode voltage generated by the dual converters is nearly an order of magnitude lower than that generated by single VSI.

#### VIII. CONCLUSION

In this paper, a generalized carrier based pulse width modulation technique has been developed for open-end winding

Fig. 20. Experimental results for Dual two-level inverter (gray patch in top graphs indicates the length of one cycle of output fundamental frequency) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (b) Negative end pole voltages (top three graphs) and CMV (bottom graph) [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (d)Positive end pole voltages and CMV (zoomed) [X axis:  $20\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)] (e) Negative end pole voltages and CMV (zoomed) [X axis:  $20\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)] (f) Phase voltages and CMV across load (zoomed) [X axis:  $20\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)]

Fig. 21. Experimental results (Dual two-level inverter) (a) Three phase load currents (top graph) and circulating current (bottom graph) [X axis: 2 ms/div, Y axis: 1 A/div] (b) Fourier spectrum of voltage  $v_{\rm AA'}$  across load phase A using carrier based method (top graph) and space vector method (bottom graph) [X axis: 5 kHz/div, Y axis: 10 V/div]

Fig. 22. Diagram of the experimental setup for dual matrix converter

PWM ac drive. A detailed analysis shows the relationship and a comparison in terms of computational effort of the proposed method with the existing space vector based modulation technique. The superior performance of the proposed carrier based method in terms of resources consumed and execution time has been confirmed by implementing both algorithms on an FPGA based real time control platform. Finally, the simulation results verified by hardware have been presented to demonstrate the proposed technique applied to both two-level and matrix converter cases.

#### REFERENCES

[1] S. Chen, T. Lipo, and D. Fitzgerald, "Source of induction motor bearing currents caused by pwm inverters," *Energy Conversion, IEEE Transactions on*, vol. 11, no. 1, pp. 25 –32, mar 1996.

Fig. 23. Experimental results for Dual matrix inverter (gray patch in top graphs indicates the length of one cycle of output fundamental frequency) (a) Positive end pole voltages (top three graphs) and common-mode voltage (CMV) (bottom graph) [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (b) Negative end pole voltages (top three graphs) and CMV (bottom graph) [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (c) Voltages across load phases (top three graphs) and CMV (bottom graph) across load [X axis: 2 ms/div (top three graphs) 200  $\mu$ s/div (bottom graph), Y axis: 50 V/div] (d)Positive end pole voltages and CMV [X axis: 20 $\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)] (e)Negative end pole voltages and CMV [X axis: 20 $\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)] (f) Phase voltages and CMV across load [X axis: 20 $\mu$ s/div, Y axis: 20 V/div (top three waveforms) 50V/div (bottom waveform)]

Fig. 24. Experimental results (dual matrix converter) (a) Input current and voltage of phase a [X axis: 5 ms/div, Y axis: 20V/div, 2A/div] (b) Three phase load currents (top graph) and circulating current (bottom graph) [X axis: 2 ms/div, Y axis: 1 A/div] (c) Fourier spectrum of voltage  $v_{AA'}$  across load phase A using carrier based method (top graph) and space vector method (bottom graph) [X axis: 5 kHz/div, Y axis: 10 V/div]

- [2] J. Erdman, R. Kerkman, D. Schlegel, and G. Skibinski, "Effect of pwm inverters on ac motor bearing currents and shaft voltages," *Industry Applications, IEEE Transactions on*, vol. 32, no. 2, pp. 250 –259, mar/apr 1996.

- [3] S. Chen, T. Lipo, and D. Fitzgerald, "Modeling of motor bearing currents in pwm inverter drives," *Industry Applications, IEEE Transactions on*, vol. 32, no. 6, pp. 1365–1370, 1996.

- [4] E. Zhong and T. Lipo, "Improvements in emc performance of inverter-fed motor drives," *Industry Applications, IEEE Transactions on*, vol. 31, no. 6, pp. 1247–1256, 1995.

- [5] U. Shami and H. Akagi, "Experimental discussions on a shaft end-toend voltage appearing in an inverter-driven motor," *Power Electronics*, *IEEE Transactions on*, vol. 24, no. 6, pp. 1532–1540, 2009.

- [6] H. Akagi and S. Tamura, "A passive emi filter for eliminating both bearing current and ground leakage current from an inverter-driven motor," *Power Electronics, IEEE Transactions on*, vol. 21, no. 5, pp. 1459–1469, Sept 2006.

- [7] H. Akagi and T. Doumoto, "An approach to eliminating high-frequency shaft voltage and ground leakage current from an inverter-driven motor,"

- Industry Applications, IEEE Transactions on, vol. 40, no. 4, pp. 1162–1169, 2004.

- [8] S. Ogasawara and H. Akagi, "Circuit configurations and performance of the active common-noise canceler for reduction of common-mode voltage generated by voltage-source pwm inverters," in *Industry Appli*cations Conference, 2000. Conference Record of the 2000 IEEE, vol. 3, 2000, pp. 1482–1488 vol.3.

- [9] A. Julian, G. Oriti, and T. Lipo, "Elimination of common-mode voltage in three-phase sinusoidal power converters," *Power Electronics, IEEE Transactions on*, vol. 14, no. 5, pp. 982–989, 1999.

- [10] H.-D. Lee and S.-K. Sul, "Common-mode voltage reduction method modifying the distribution of zero-voltage vector in pwm converter/inverter system," *Industry Applications, IEEE Transactions on*, vol. 37, no. 6, pp. 1732–1738, Nov 2001.

- [11] A. Ruderman and B. Reznikov, "Evaluation of motor pwm loss increase due to zero common-mode voltage modulation strategy of multilevel converter," in *Power Electronics and Motion Control Conference* (EPE/PEMC), 2010 14th International, 2010, pp. T3–66–T3–72.

- [12] F. Wang, "Motor shaft voltages and bearing currents and their reduction

Fig. 25. High Frequency frequency spectrum of common-mode voltages (CMV) (experimental results): Single VSI (top graph), Differential CMV (Dual matrix converter) (Second graph), Average CMV (Dual matrix converter) (Third graph), Differential CMV (Dual two-level inverter) (Fourth graph), Average CMV (Dual two-level inverter) (Bottom graph)

- in multilevel medium-voltage pwm voltage-source-inverter drive applications," *Industry Applications, IEEE Transactions on*, vol. 36, no. 5, pp. 1336 –1341, sep/oct 2000.

- [13] H. Zhang, A. Von Jouanne, S. Dai, A. Wallace, and F. Wang, "Multilevel inverter modulation schemes to eliminate common-mode voltages," *Industry Applications, IEEE Transactions on*, vol. 36, no. 6, pp. 1645– 1653, 2000.

- [14] M. Renge and H. Suryawanshi, "Five-level diode clamped inverter to eliminatecommon mode voltage and reduce dv/dt inmedium voltage rating induction motor drives," *Power Electronics, IEEE Transactions on*, vol. 23, no. 4, pp. 1598–1607, 2008.

- [15] P. C. Loh, D. Holmes, Y. Fukuta, and T. Lipo, "Reduced common-mode modulation strategies for cascaded multilevel inverters," *Industry Applications, IEEE Transactions on*, vol. 39, no. 5, pp. 1386–1395, 2003.

- [16] I. Takahashi and Y. Ohmori, "High-performance direct torque control of an induction motor," *Industry Applications, IEEE Transactions on*, vol. 25, no. 2, pp. 257–264, 1989.

- [17] H. Stemmler and P. Guggenbach, "Configurations of high-power voltage source inverter drives," in *Power Electronics and Applications*, 1993., Fifth European Conference on, 1993, pp. 7–14 vol.5.

- [18] T. Kawabata, E. Ejiogu, Y. Kawabata, and K. Nishiyama, "New openwinding configurations for high-power inverters," in *Industrial Electron*ics, 1997. ISIE '97., Proceedings of the IEEE International Symposium on, vol. 2, 1997, pp. 457–462 vol.2.

- [19] M. R. Baiju, K. Mohapatra, R. S. Kanchan, and K. Gopakumar, "A dual two-level inverter scheme with common mode voltage elimination for an induction motor drive," *Power Electronics, IEEE Transactions on*, vol. 19, no. 3, pp. 794–805, 2004.

- [20] A. von Jauanne and H. Zhang, "A dual-bridge inverter approach to eliminating common-mode voltages and bearing and leakage currents," *Power Electronics, IEEE Transactions on*, vol. 14, no. 1, pp. 43–48, 1999.

- [21] R. Gupta, K. Mohapatra, A. Somani, and N. Mohan, "Direct-matrix-converter-based drive for a three-phase open-end-winding ac machine with advanced features," *Industrial Electronics, IEEE Transactions on*, vol. 57, no. 12, pp. 4032–4042, 2010.

- [22] R. S. Kanchan, P. N. Tekwani, and K. Gopakumar, "Three-level inverter scheme with common mode voltage elimination and dc link capacitor voltage balancing for an open-end winding induction motor drive," *Power Electronics, IEEE Transactions on*, vol. 21, no. 6, pp. 1676–1683, 2006.

- [23] G. Mondal, K. Gopakumar, P. N. Tekwani, and E. Levi, "A reduced-switch-count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive," *Industrial Electronics*, *IEEE Transactions on*, vol. 54, no. 4, pp. 2344–2351, 2007.

- [24] P. N. Tekwani, R. S. Kanchan, and K. Gopakumar, "A dual five-level inverter-fed induction motor drive with common-mode voltage elimination and dc-link capacitor voltage balancing using only the switching-state redundancy x2014;part i," *Industrial Electronics, IEEE Transactions on*, vol. 54, no. 5, pp. 2600–2608, 2007.

- [25] ——, "A dual five-level inverter-fed induction motor drive with common-mode voltage elimination and dc-link capacitor voltage balancing using only the switching-state redundancy x2014;part ii," *Industrial Electronics, IEEE Transactions on*, vol. 54, no. 5, pp. 2609–2617, 2007.

- [26] G. Mondal, K. Sivakumar, R. Ramchand, K. Gopakumar, and E. Levi, "A dual seven-level inverter supply for an open-end winding induction motor drive," *Industrial Electronics, IEEE Transactions on*, vol. 56, no. 5, pp. 1665–1673, 2009.

- [27] S. Lakshminarayanan, G. Mondal, P. N. Tekwani, K. Mohapatra, and K. Gopakumar, "Twelve-sided polygonal voltage space vector based multilevel inverter for an induction motor drive with common-mode voltage elimination," *Industrial Electronics, IEEE Transactions on*, vol. 54, no. 5, pp. 2761–2768, 2007.

- [28] B. McGrath, D. Holmes, and T. Lipo, "Optimized space vector switching sequences for multilevel inverters," *Power Electronics, IEEE Transactions on*, vol. 18, no. 6, pp. 1293–1301, Nov 2003.

- [29] J. S. Kim and S. K. Sul, "A novel voltage modulation technique of the space vector pwm," in *Proc. IPEC95 Conference, Yokohama, Japan*, 1995, p. 742747.

- [30] P. Kiatsookkanatorn and S. Sangwongwanich, "A unified pwm method for matrix converters and its carrier-based realization using dipolar modulation technique," *Industrial Electronics, IEEE Transactions on*, vol. 59, no. 1, pp. 80–92, 2012.

- [31] K. Mohapatra, P. Jose, A. Drolia, G. Aggarwal, and S. Thuta, "A novel carrier-based pwm scheme for matrix converters that is easy to implement," in *Power Electronics Specialists Conference*, 2005. PESC '05. IEEE 36th, June 2005, pp. 2410–2414.

- [32] D.-W. Kang, Y.-H. Lee, B.-S. Suh, C.-H. Choi, and D.-S. Hyun, "An improved carrier-based svpwm method using leg voltage redundancies in generalized cascaded multilevel inverter topology," *Power Electronics*, *IEEE Transactions on*, vol. 18, no. 1, pp. 180–187, 2003.

- [33] Y.-H. Lee, R. young Kim, and D.-S. Hyun, "A novel svpwm strategy considering dc-link balancing for a multi-level voltage source inverter," in *Applied Power Electronics Conference and Exposition*, 1999. APEC '99. Fourteenth Annual, vol. 1, 1999, pp. 509–514 vol.1.

- [34] A. Videt, P. Le Moigne, N. Idir, P. Baudesson, and X. Cimetiere, "A new carrier-based pwm providing common-mode-current reduction and dc-bus balancing for three-level inverters," *Industrial Electronics, IEEE Transactions on*, vol. 54, no. 6, pp. 3001–3011, 2007.

- [35] N. Bodo, E. Levi, and M. Jones, "Investigation of carrier-based pwm techniques for a five-phase open-end winding drive topology," *Industrial Electronics, IEEE Transactions on*, vol. 60, no. 5, pp. 2054–2065, 2013.

- [36] A. Iqbal and S. Moinuddin, "Comprehensive relationship between carrier-based pwm and space vector pwm in a five-phase vsi," *Power Electronics, IEEE Transactions on*, vol. 24, no. 10, pp. 2379–2390, 2009.

- [37] W. Yao, H. Hu, and Z. Lu, "Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter," *Power Electronics*, *IEEE Transactions on*, vol. 23, no. 1, pp. 45–51, 2008.

- [38] R. Baranwal, K. Basu, and N. Mohan, "Dual two level inverter carrier svpwm with zero common mode voltage," in *Power Electronics, Drives* and Energy Systems (PEDES), 2012 IEEE International Conference on, 2012, pp. 1–6.

- [39] L. Huber and D. Borojevic, "Space vector modulated three-phase to three-phase matrix converter with input power factor correction," *Indus*try Applications, IEEE Transactions on, vol. 31, no. 6, pp. 1234–1246, Nov 1995.

- [40] A. Somani, R. Gupta, K. Mohapatra, and N. Mohan, "On the causes of circulating currents in pwm drives with open-end winding ac machines,"

Industrial Electronics, IEEE Transactions on, vol. 60, no. 9, pp. 3670–3678, 2013

**Rohit Baranwal** received his B.Tech. degree in Electrical Engineering from Indian Institute of Technology Roorkee in 2008. Currently, he is pursuing a PhD in Electrical Engineering at University of Minnesota. His areas of interest are power electronics and its applications in renewable energy sources.

Kaushik Basu received the B.E. degree from the Bengal Engineering and Science University, Shibpore, India, in 2003, the M.S. degree in electrical engineering from the Indian Institute of Science, Bangalore, India, in 2005, and the Ph.D. degree in electrical engineering from the University of Minnesota, Minneapolis, in 2012, respectively. He was a Design Engineer with ColdWatt India in 2006. He is currently a Electronics and Control Engineer with Dynapower Corporation, South Burlington, VT, USA. His research interests include high-frequency

link converters, pulse width modulation techniques, and grid tied converters with storage and renewable energy sources

Ned Mohan received the B.Tech. degree from the Indian Institute of Technology (IIT), Kharagpur, India, in 1967, the M.S. degree in electrical engineering from the University of New Brunswick, Fredericton, NB, Canada, in 1969, and the M.S. degree in nuclear engineering and the Ph.D. degree in electrical engineering from the University of Wisconsin, Madison, WI, USA, in 1972 and 1973, respectively. He is currently the Oscar A. Schott Professor of power electronics with the University of Minnesota, Minneapolis, MN, USA, where he

has been engaged in teaching since 1976. He has numerous patents and publications in the field of power electronics, electric drives, and power systems. He has authored or coauthored five textbooks, one of which has been translated into six languages. He has graduated 35 Ph.D.s as of 2013. Dr. Mohan received the 2008 IEEE PES Outstanding Educator Award, 2010 IEEE Undergraduate Teaching Award, 2010 UWIG Achievement Award from Utility Wind Integration Group, 2011 Distinguished Alumnus Award from IIT Kharagpur, and 2012 IEEE Power and Energy Society Ramakumar Family Renewable Energy Excellence Award. In 2013, he received the Innovative Program Award from the ECE Department Heads Association made up of over 250 universities in the United States.