# A Three-Phase Three-Level Isolated DC–AC Converter With Line Frequency Unfolding

Anirban Pal<sup>®</sup>, Student Member, IEEE, and Kaushik Basu, Senior Member, IEEE

Abstract—A three-level three-phase single-stage high-frequency link dc-ac converter is reported in this article for grid integration of photovoltaic sources. The proposed topology employs two three-level neutral point clamp (NPC) half-bridge legs on the dc side. The advantages of using three-level legs over conventional two level are: 1) the three-level legs can be implemented with the devices with lower blocking voltage which are economical; and 2) the low voltage blocking devices have lower ON-state drop and lower turn ON-OFF energy losses compared to high voltage blocking devices used in a two-level leg. These help to improve the converter efficiency. The sinusoidal pulsewidth modulation is implemented with the three-level NPC legs. The modulation strategy ensures reduced neutral current drawn by the NPC legs. The inner switches of the NPC legs are zero voltage switched. The turn-ON transitions of the outer switches are with zero current. The proposed solution employs two high-frequency transformers to provide galvanic isolation which results in compact, low cost isolated converter solution. The intermediate dc link is pulsating and does not require any filtering. A low-frequency unfolder is employed to generate line frequency ac from pulsating dc. The switching loss of the unfolder is negligible. The proposed topology can support stand-alone load up to  $\pm 0.866$  PF. The converter operation is verified on a 2-kW hardware prototype.

Index Terms—DC-AC converter, high-frequency link, line frequency unfolding, phase shift modulation, single-stage, three-level neutral point clamp (NPC) inverter, zero current switching (ZCS), zero voltage switched (ZVS).

#### I. INTRODUCTION

THE pulsewidth modulated (PWM) single-stage high-frequency link (HFL) dc- $3\phi$  ac converters are gaining attention for applications such as grid integration of renewable energy sources [1], [2], energy storage system [3], electric or hybrid electric vehicle [4], etc. The single-stage converters do not use interstage bulky dc capacitors which are unreliable. To provide galvanic isolation high-frequency transformers (HFTs) are used which results in high-power density, economical converter solution. In the literature, the PWM single-stage HFL dc- $3\phi$  ac converters are classified into two major categories—cyclo-converter-type HFL (CHFL) [5]–[7] and rectifier-type

Manuscript received January 24, 2020; accepted March 19, 2020. Date of publication April 1, 2020; date of current version July 20, 2020. This work was supported by the Department of Science and Technology, Government of India, under the Project "Development of an advanced System-On-Chip (SoC) based embedded controller for power electronic converters." Recommended for publication by Associate Editor Y. Xing. (Corresponding author: Anirban Pal.)

The authors are with the Department of Electrical Engineering, Indian Institute of Science, Bangalore 560012, India (e-mail: anirbanp@iisc.ac.in; kbasu@iisc.ac.in).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2020.2984698

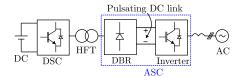

Fig. 1. Unidirectional single-stage RHFL inverter.

HFL (RHFL) [8], [9]. In CHFL topology, H-bridge is used to generate high frequency (HF) ac from input dc. The HF ac is fed to HFT. A cyclo-converter is employed in the secondary of the HFT to generate line frequency ac from the HF ac. In an RHFL topology, the cyclo-converter of the CHFL is replaced with an active rectifier followed by a voltage source inverter (VSI). The dc link between the rectifier and inverter stage is pulsating. In applications such as grid integration of renewables or fuel cells, where the active power flow is mostly from input dc to ac, the unidirectional PWM RHFL dc- $3\phi$  ac topologies [10]–[15] are becoming popular. In an unidirectional RHFL topology, the rectifier stage is implemented with diode bridge rectifier instead of active switches (see Fig. 1) thus reducing active component count and additional driving circuitry. As seen in Fig. 1, these converters have three parts—dc side converter (DSC), ac side converter (ASC) and HFT. Though unidirectional, but these converters might need to support  $\pm 0.9/0.95$  PF operation at the grid end as per grid requirements [16]. The converter proposed in [10]–[13] support operation up to  $\pm 0.866$  PF. These converters employ a hybrid modulation strategy where the ASC inverter is HF switched for one-third of the line cycle (partial unfolding). The unidirectional topologies presented in [14] and [15], though achieve complete line frequency unfolding of the ASC, they can only support unity power factor (UPF) operation. Additional shunt compensator is needed to support the reactive power demand at the grid end. The unidirectional RHFL topologies discussed so-far employ two-level structure on the DSC to generate HF ac from input dc. The three-level NPC converters are considered as an alternative to the standard two-level VSIs in low voltage applications [17], [18] because of increased efficiency at higher switching frequencies along with improved output harmonic spectrum and reduced electromagnetic interference (EMI). With same input dc voltage, the three-level legs can be implemented with lower blocking voltage devices which are economical. The low blocking voltage devices have lower ON-state drop and lower turn ON-OFF energy losses compared to high voltage blocking devices used in a two-level leg [17] hence the improvement in the efficiency. The idea can

$0885\text{-}8993 \ @\ 2020\ IEEE.\ Personal\ use\ is\ permitted,\ but\ republication/redistribution\ requires\ IEEE\ permission.$  See https://www.ieee.org/publications/rights/index.html for more information.

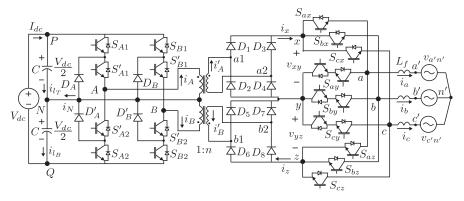

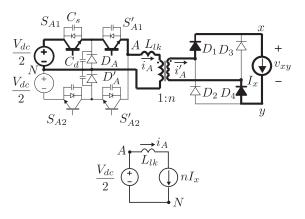

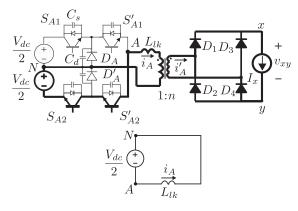

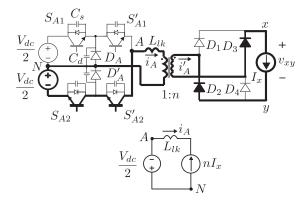

Fig. 2. Configuration of the proposed inverter.

be extended to isolated dc-dc and dc-ac converter topologies. A three-level zero voltage switched (ZVS) PWM dc-dc converter was first introduced in [19], where the input two-level H-bridge of a phase shifted full bridge (PSFB) converter is replaced with a three-level NPC leg. A passive auxiliary circuit is proposed in [20], which resets the primary circulating current in zero state thereby improving the efficiency. For high power application, three-phase, three-level dc-dc converters are proposed in [21] and [22]. Like a PSFB, the ZVS of a three-level dc-dc converter is also load dependent and at light load the converter is hard switched. Even hard switched, the light-load efficiency of a three-level dc-dc converter is higher than a similarly rated two-level counterpart as the blocking voltage of the devices are half and have better switching characteristics [23], [24]. In [25], a unidirectional RHFL inverter topology is reported where the DSC has three, three-level NPC legs. But the converter can only support UPF operation.

In this article, a three-level three-phase single stage HFL dc—ac converter is proposed (see Fig. 2). The proposed solution is unique w.r.t the above discussed topologies because it has all the following features together.

- 1) On the DSC, the converter has two three-level NPC half-bridge legs to generate HF ac from the input dc.

- 2) The ASC achieves line frequency unfolding.

- 3) The proposed topology can supply stand-alone load up to  $\pm~0.866$  power factor.

Additionally, the converter has the following key features.

- 1) Sinusoidal pulsewidth modulation (PWM) is implemented with the dc side three-level legs. But the modulation strategy and the switching scheme of the NPC legs are completely different from the conventional PWM strategy applied to a  $3\phi$ , three-level NPC inverter which results in generation of line frequency ac from input dc. The proposed strategy generates PWM HF ac across the transformer primaries using the two three-level, NPC legs.

- 2) Suggested modulation strategy ensures reduced neutral current drawn by the three-level legs.

- 3) The inner switches of the three-level legs are zero voltage switched (ZVS) over complete line cycle.

- 4) zero current switching (ZCS) of the outer switches are ensured.

- 5) Interstage dc link is pulsating and does not employ filter capacitor.

- 6) Low frequency switching results in negligible switching loss of the unfolder.

- 7) The HF galvanic isolation provides high power density, economical converter solution.

The article is organized as follows. The modulation strategy of the converter is discussed in Section II. In Section III, the detailed switching process of the three-level legs are described. Experimental validation of the converter operation is presented in Section IV.

#### II. CONVERTER MODULATION TECHNIQUE

As shown in Fig. 2, the proposed dc–ac converter employs two three-level neutral point clamp (3 L-NPC) half-bridge legs on the dc side. Two HFTs, each with a turns ratio 1:n, provide the galvanic isolation. The primary windings of the HFTs are connected between the poles of the NPC half-bridge legs and the neutral point, N as seen in Fig. 2. The neutral point N is obtained by connecting two capacitors (C) in series across the input dc bus  $(V_{

m dc})$ . The secondary output of each HFT is fed to a full-bridge rectifier. The output ports of the two rectifiers are connected in series to obtain a three-level dc link. The proposed topology does not employ dc link filter capacitors and hence the three-level dc link is pulsating. To obtain three-phase line frequency ac from the pulsating dc link, an unfolder with six two-quadrant and three four-quadrant switches, is employed. The three-phase output of the converter is connected to a balanced three-phase source through line filters  $(L_f)$ .

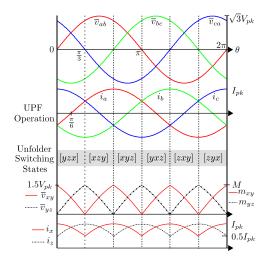

To generate the balanced three-phase line frequency average pole voltages (see Fig. 3),  $\overline{v}_{ab} = \sqrt{3}V_{pk}\sin(\omega_o t = \theta)$ ,  $\overline{v}_{bc} = \sqrt{3}V_{pk}\sin(\theta - \frac{2\pi}{3})$  and  $\overline{v}_{ca} = \sqrt{3}V_{pk}\sin(\theta + \frac{2\pi}{3})$  with angular frequency  $\omega_o = 2\pi f_o$ , the unfolder is switched six times over a line cycle. The switching states of the unfolder is given in Table I. The unfolder poles (a,b,c) can be connected to the node x through the switches  $S_{(a,b,c)x}$ , node y through the switches  $S_{(a,b,c)y}$ , and node z through the switches  $S_{(a,b,c)z}$ , respectively. Unfolder switching state [yzx] indicates that the pole a is connected to node y through  $S_{ay}$ , the pole b is connected to node z through z0 and the pole z1 is connected to node z3 through z1 in the pole z2 is connected to node z3 through z2 is connected to node z3 through z3 and the pole z3 is connected to node z4 through z3 and the pole z4 is connected to node z5 through z4 is connected to node z5 through z5 is connected to node z5 through z6 is connected to node z6 through z6 is connected to node z8 is connected t

Fig. 3. Modulating strategy of the proposed converter.

TABLE I UNFOLDER SWITCHING STATES

| $\theta$ | $[0,\frac{\pi}{3}]$ | $[\frac{\pi}{3}, \frac{2\pi}{3}]$ | $[\frac{2\pi}{3},\pi]$ | $[\pi, \frac{4\pi}{3}]$ | $[\frac{4\pi}{3}, \frac{5\pi}{3}]$ | $[\frac{5\pi}{3}, 2\pi]$ |

|----------|---------------------|-----------------------------------|------------------------|-------------------------|------------------------------------|--------------------------|

| State    | [yzx]               | [xzy]                             | [xyz]                  | [yxz]                   | [zxy]                              | [zyx]                    |

TABLE II RECTIFIER OUTPUT VOLTAGES AND CURRENTS

| Unfolder State      | [yzx]               | [xzy]                | [xyz]               | [yxz]               | [zxy]               | [zyx]               |

|---------------------|---------------------|----------------------|---------------------|---------------------|---------------------|---------------------|

| $\overline{v}_{xy}$ | $\overline{v}_{ca}$ | $-\overline{v}_{ca}$ | $\overline{v}_{ab}$ | $\overline{v}_{ab}$ | $\overline{v}_{bc}$ | $\overline{v}_{bc}$ |

| $\overline{v}_{yz}$ | $\overline{v}_{ab}$ | $\overline{v}_{bc}$  | $\overline{v}_{bc}$ | $\overline{v}_{ca}$ | $\overline{v}_{ca}$ | $\overline{v}_{ab}$ |

| $i_x$               | $i_c$               | $i_a$                | $i_a$               | $i_b$               | $i_b$               | $i_c$               |

| $i_z$               | $-i_b$              | $-i_b$               | $-i_c$              | $-i_c$              | $-i_a$              | $-i_a$              |

through  $S_{cx}$ . Similarly, the other states are also defined. Following the switching states, the unfolder two quadrant switches are switched at line frequency whereas the four quadrant switches are switched at twice of the line frequency hence incurring negligible switching loss.

From the switching states of the unfolder, the rectifier average output voltages  $(\overline{v}_{xy} \text{ and } \overline{v}_{yz})$  and currents  $i_x, i_z$  are obtained and are given in Table II.  $i_{a,b,c}$  are the sinusoidal line currents with negligible ripple, supplied to the load.

For example, when the switching state is [yzx], the unfolder switches  $S_{ay}$ ,  $S_{bz}$ , and  $S_{cx}$  are ON. Hence, the rectifier output port xy is connected across the pole terminals ca and yzis connected across ab. Thus,  $\overline{v}_{xy} = \overline{v}_{ca}$ ,  $\overline{v}_{yz} = \overline{v}_{ab}$  and the rectifier output currents  $i_x=i_c$  and  $i_z=-i_b$ . To generate the average output rectifier voltages as given in Table II, the modulation signals of the dc side 3 L-NPC legs,  $m_{xy} = \frac{\overline{v}_{xy}}{n(V_{\rm dc}/2)}$

and  $m_{yz}=\frac{\overline{v}_{yz}}{n(V_{\rm dc}/2)}$  are shown in Fig. 3. M is defined as  $M=\frac{3V_{pk}}{nV_{\rm dc}} \mbox{ and } M\in[0,1].$  The 3 L-NPC legs are HF switched to generate the sinusoidal

$$M = \frac{3V_{pk}}{nV_{dc}}$$

and  $M \in [0, 1]$

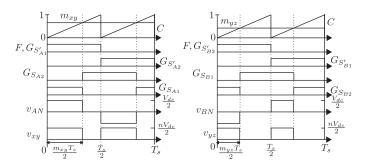

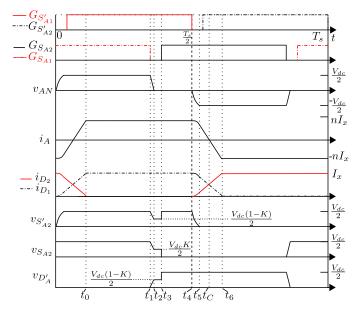

pulsewidth modulated HF ac across the transformer primaries. The modulation strategy is shown in Fig. 4. A signal F with period  $T_s$  and 50% duty ratio is considered over which the transformer flux is balanced. F is assigned to be the gating signals

Modulation of dc side three-level legs.

Fig. 5. Neutral and dc-link capacitor currents of the dc side three-level NPC inverter.

of  $S_{A1}'(G_{S_{A1}'})$  and  $S_{B2}'(G_{S_{B2}'})$ .  $S_{A2}'$  is switched complementary with  $S_{A1}'$ . Similarly,  $S_{B1}'$  is complementary switched with  $S_{B2}'$ . The outer switches of the legs,  $(S_{A1} - S_{A2})$  and  $(S_{B1} - S_{B2})$ , are also complementary switched. A unipolar saw-tooth carrier, C, with period  $\frac{T_s}{2}$  is considered which is aligned with F. The modulation signals  $m_{xy}$  and  $m_{yz}$  are compared with C to obtained the gating signals of  $S_{A2}$  and  $S_{B1}$ , respectively. The gating pulses of  $S_{A2}$  and  $S_{B1}$  are also square wave with period  $T_s$ and 50% duty ratio. But these signals are phase shifted by  $\frac{m_{xy}T_s}{2}$ and  $\frac{m_{yz}T_s}{2}$  w.r.t  $G_{S'_{A_1}}$  and  $G_{S'_{B_2}}$ , respectively. The modulation strategy applies HF ac (HFac) voltages,  $v_{AN}$  and  $v_{BN}$ , across the transformer primaries with voltage levels  $\pm \frac{V_{\rm dc}}{2}$  and 0 and pulsewidths  $\frac{m_{xy}T_s}{2}$  and  $\frac{m_{yz}T_s}{2}$ , respectively, as seen in Fig. 4. In the secondary of the HFTs, the rectifiers rectify the HFac inputs. The output of the rectifiers,  $v_{xy}$  and  $v_{yz}$  are pulsating dc with voltage levels  $+\frac{nV_{dc}}{2}$  and 0.

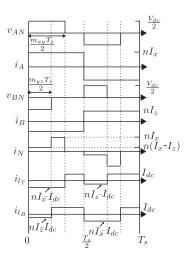

The above switching scheme ensures reduced neutral current  $i_N$  drawn by the 3 L-NPC legs. The scheme helps to reduce the rms current of the dc link capacitors. Fig. 5 shows the applied primary voltages, primary currents, and the neutral link current  $i_N$  over a switching cycle. The polarities of the applied voltages across the transformer primaries in a half switching cycle are opposite. Hence the transformer winding currents  $i_A$ and  $i_B$  also have opposite polarities. In Fig. 5, the waveforms are shown at a switching instant when  $m_{xy} > m_{yz}$ .  $i_A$  and  $i_B$

have magnitudes of  $nI_x$  and  $nI_z$ , respectively.  $I_x$  and  $I_z$  are the magnitudes of rectifier output current  $i_x$  and  $i_z$ , respectively, and are considered as constant over a switching cycle. For UPF operation, in the switching state [yzx] ( $\theta \in 0, \frac{\pi}{3}$ ),  $i_x = I_{pk}\cos\theta$  and  $i_y = I_{pk}\sin(\theta + \frac{\pi}{6})$  (see Fig. 3). As seen in Fig. 5, during  $0 < t < \frac{m_{yz}T_s}{2}$ ,  $i_N = i_A + i_B = n(I_x - I_y)$ . During  $\frac{m_{yz}T_s}{2} < t < \frac{m_{xy}T_s}{2}$ , transformer terminals BN are shorted through leg B diode  $D_B'$  and switch  $S_{B2}'$  and hence  $i_N = i_A = nI_x$ . During  $\frac{m_{xy}T_s}{2} < t < \frac{T_s}{2}$ , both the transformer primary terminals are shorted through one diode and switch pair. Hence,  $i_N = 0$ . Similarly,  $i_N$  can be derived in other half of the switching cycle. The waveform of  $i_N$  has symmetry over  $\frac{\pi}{6}$ . The rms of neutral current  $i_{N,\rm rms}$  at UPF operation of the converter is given as

$i_{N,\mathrm{rms}}$

$$= \sqrt{\frac{6}{\pi} \int_0^{\frac{\pi}{6}} \left[ n^2 (i_x - i_z)^2 m_{yz} + (ni_x)^2 (m_{xy} - m_{yz}) \right] d\theta}$$

$$= 0.709 \sqrt{M} n I_{nk}. \tag{1}$$

In the switching state [yzx],  $m_{xy} = 1.15M\cos(\theta + \frac{\pi}{6})$  and  $m_{yz} = 1.15M\sin\theta$  (see Fig. 3).

Similarly, the dc link capacitor rms currents at UPF operation is given as

$$i_{l_T,\text{rms}} = i_{l_B,\text{rms}} = nI_{pk}\sqrt{(0.458 - 0.243M)M}.$$

(2)

Though the proposed topology has diode rectifiers in the secondary and does not employ any dc-link capacitor after the rectifier stage, it can support up to  $30^{\circ}$  leading and lagging power factor stand-alone load. The rectifier output currents  $i_x$  and  $i_z$  are positive instantaneously. Following Table II and Fig. 3 in state [xzy], it can be seen that  $i_x(=i_a)$  becomes negative when  $i_a$  lags more than  $30^{\circ}$ . Similarly  $i_z(=-i_b)$  becomes negative when  $i_b$  leads more than  $30^{\circ}$ . The negative link currents cannot be supported by the rectifiers and hence, the converter operation is power factor restricted.

#### III. OPERATION OF 3 L-NPC LEGS

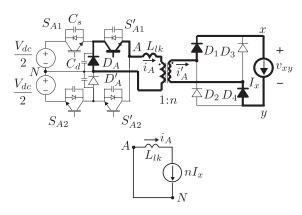

Though HF switched, the 3 L-NPC legs are soft-switched without additional auxiliary circuits. The operation of the 3 L-NPC legs are analyzed in details over a switching cycle  $(T_s)$  for UPF operation of the converter. The operation of both the legs are independent but similar, hence only leg A is considered for further discussion. The operation is described when the unfolder is in state [yzx]. Similar strategy is followed in other states. In state [yzx], the rectifier output current  $i_x = i_c$  (see Fig. 3). As the line currents  $(i_{a,b,c})$  are properly filtered and slowly varying,  $i_x$ can be considered as constant current sink over  $T_s$ . Hence after the rectifier stage, the unfolder can be modeled as current sinks. The converter operation is analyzed considering the 3 L-NPC leg device  $(C_s)$  and diode  $(C_d)$  capacitances and the transformer leakage inductance (seen from primary)  $L_{lk}$ . Simplified circuit associated with leg A operation is shown in Fig. 7. The key switching transition waveforms are shown in Fig. 6.

Fig. 6. Important switching waveforms over  $T_s$ .

Fig. 7. Mode 1: Circuit diagram and equivalent circuit.

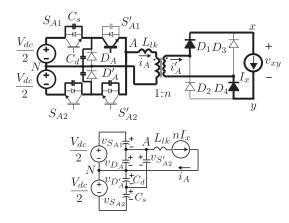

#### A. Mode 1 ( $t_0 < t < t_1$ , Fig. 7)

Top two switches,  $S_{A1}$  and  $S'_{A1}$ , of the 3 L-NPC leg A are conducting which apply  $\frac{V_{\rm dc}}{2}$  across the transformer primary terminals AN. In the secondary, the diodes  $D_1$  and  $D_4$  are conducting. The circuit is transferring active power from input to the load. The equivalent circuit is shown in Fig. 7. The primary current is  $i_A = nI_x$ . The diode  $D_A$  and bottom two switches  $S'_{A2}$  and  $S_{A2}$  are blocking  $\frac{V_{\rm dc}}{2}$  (see Fig. 6).

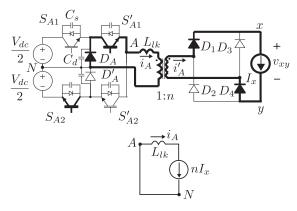

B. Mode 2

$$(t_1 < t < t_2, Fig. 8)$$

This mode begins at  $t_1$  when  $S_{A1}$  is turned OFF. The voltage across  $S_{A1}$  rises slowly due to device capacitance  $C_s$ . This helps to reduce turn-OFF loss of  $S_{A1}$ .  $i_A$  charges the device and diode capacitances of  $S_{A1}$  and  $D_A'$ , respectively. The capacitances of  $D_A$ ,  $S_{A2}'$ , and  $S_{A2}$  are being discharged. The equivalent circuit is shown in Fig. 8. The circuit equations are given as

$$v_{S_{A1}} + v_{D_A} = \frac{V_{dc}}{2}$$

$v_{S_{A1}} + v_{S'_{A2}} + v_{S_{A2}} = V_{dc}$

Fig. 8. Mode 2: Circuit diagram and equivalent circuit.

$$v_{S_{A2}} + v_{D'_{A}} = \frac{V_{dc}}{2}$$

$$C_{s} \frac{dv_{S_{A1}}}{dt} = C_{d} \frac{dv_{D_{A}}}{dt} + C_{s} \frac{dv_{S'_{A2}}}{dt} + nI_{x}$$

$$C_{s} \frac{dv_{S'_{A2}}}{dt} + C_{d} \frac{dv_{D'_{A}}}{dt} = C_{s} \frac{dv_{S_{A2}}}{dt}.$$

(3)

Solving (3), the voltage dynamics across the devices are given as

$$v_{S_{A1}}(t) = \left(\frac{2C_s + C_d}{C_s + C_d}\right) \frac{nI_x(t - t_1)}{3C_s + C_d}$$

$$v_{S'_{A2}}(t) = \frac{V_{dc}}{2} - \frac{nI_x(t - t_1)}{3C_s + C_d}$$

$$v_{S_{A2}}(t) = \frac{V_{dc}}{2} - \left(\frac{C_s}{C_s + C_d}\right) \frac{nI_x(t - t_1)}{3C_s + C_d}.$$

(4)

At  $t_2$ ,  $v_{S_{A1}} = \frac{V_{\rm dc}}{2}$ . The voltage across  $D_A$  is zero and is forward biased. The interval  $(t_2 - t_1)$  is given in (5). At  $t_2$  the blocking voltages across  $S'_{A2}$  and  $S_{A2}$  are given as

$$(t_2 - t_1) = \frac{V_{dc}}{2} \left(\frac{C_s + C_d}{2C_s + C_d}\right) \frac{3C_s + C_d}{nI_x}$$

$$v_{S'_{A2}}(t_2) = \frac{(1 - K)V_{dc}}{2}$$

$$v_{S_{A2}}(t_2) = \frac{KV_{dc}}{2}$$

(5)

where

$$K = \frac{C_s + C_d}{2C_s + C_d}$$

. If  $C_s \gg C_d$ ,  $K = 0.5$ .

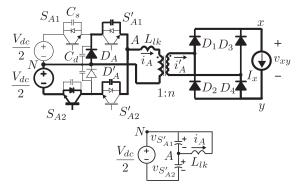

#### C. Mode 3 $(t_2 < t < t_4)$

- 1) Mode 3a ( $t_2 < t < t_3$ , Fig. 9):  $D_A$  and  $S'_{A1}$  are conducting. The transformer primary terminals A,N are shorted. In this mode, the load current free-wheels through the circuit and no active power is transferred from source to load. The mode is termed as zero state. Equivalent circuit is shown in Fig. 9.  $S_{A2}$  blocks  $\frac{KV_{\rm dc}}{2}$ . The blocking voltage of  $S'_{A2}$  and  $D'_A$  is  $\frac{(1-K)V_{\rm dc}}{2}$ . Currents through these devices and the diode are zero.

- 2) Mode 3b ( $t_3 < t < t_4$ , Fig. 10): At  $t_3$ ,  $S_{A2}$  is turned ON. As  $S_{A2}$  does not conduct current before and just after the

Fig. 9. Mode 3a: Circuit diagram and equivalent circuit.

Fig. 10. Mode 3b: Circuit diagram and equivalent circuit.

Fig. 11. Mode 4: Circuit diagram and equivalent circuit.

switching transition, the turn-ON of  $S_{A2}$  is a ZCS. The device parasitic capacitance  $C_s$  discharges through the channel of  $S_{A2}$ . As the blocking voltage was  $\frac{KV_{\rm dc}}{2}$  where K<1 and  $C_s$  is only the parasitic capacitance with small value, the loss due to capacitive discharge is negligible. After  $t_3$ , the blocking voltage of  $S'_{A2}$  and  $D'_A$  is  $\frac{V_{\rm dc}}{2}$ . The circuit continues to be in zero state with conducting  $D_A$ ,  $S'_{A1}$  and the secondary diodes  $D_1$ ,  $D_4$ .

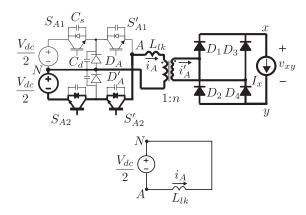

## D. Mode 4 ( $t_4 < t < t_5$ , Fig. 11)

At  $t_4$ ,  $S'_{A1}$  is turned OFF. The voltage across  $S'_{A1}$  changes slowly due to device capacitance  $C_s$  which reduces the turn-OFF loss of  $S'_{A1}$ . The pole current  $i_A$  starts charging the capacitance

Fig. 12. Mode 5: Circuit diagram and equivalent circuit.

across  $S_{A1}'$  and discharging the capacitance across  $S_{A2}'$ . Appeared voltage polarity across the transformer primary, AN is negative which forward bias the rectifier diodes  $D_2, D_3$ . Hence, the transformer secondary is shorted through the rectifier bridge. The equivalent circuit is shown in Fig. 11. The circuit equations are given as

$$v_{S'_{A1}} + v_{S'_{A2}} = \frac{V_{dc}}{2}$$

$$v_{S'_{A1}} + L_{lk} \frac{di_A}{dt} = 0$$

$$C_s(dv_{S'_{A1}}/dt - dv_{S'_{A2}}/dt) = i_A.$$

(6)

Equation (6) is solved with initial conditions  $v_{S_{A1}'}(t_4)=0$ ,  $v_{S_{A2}'}(t_4)=\frac{V_{\rm dc}}{2}$ , and  $i_A(t_4)=nI_x$ . The voltage across  $v_{S_{A1}'}$  and the current  $i_A$  are given as

$$v_{S'_{A1}}(t) = n\omega_r L_{lk} I_x \sin \omega_r (t - t_4)$$

$$i_A(t) = nI_x \cos \omega_r (t - t_4)$$

(7)

where  $\omega_r=\frac{1}{\sqrt{2L_{lk}C_s}}$ . At  $t_5$  this mode ends when  $v_{S_{A1}'}=V_{\rm dc}/2$  and  $v_{S_{A2}'}=0$ . To complete the charge–discharge of  $C_s$  across  $S_{A1,A2}'$ , the condition is given in (8). The duration  $(t_5-t_4)$  is given as

$$nI_x \ge \frac{V_{\rm dc}}{2\omega_r L_{lk}}$$

$$(t_5 - t_4) = \frac{1}{\omega_r} \sin^{-1} \left(\frac{V_{\rm dc}}{2\omega_r L_{lk} n I_x}\right). \tag{8}$$

Else, the circuit enters into a resonating oscillation mode and successive turn-ON of  $S'_{A2}$  results in hard switching.

# E. Mode 5 ( $t_5 < t < t_C$ , Fig. 12)

At  $t_5$ , when the voltage across  $S'_{A2}$  becomes zero, the antiparallel diode across  $S'_{A2}$  is forward biased and starts conducting. The equivalent circuit is shown in Fig. 12. The applied voltage across the transformer primary  $v_{AN}=-\frac{V_{\rm dc}}{2}$ .  $i_A$  changes linearly in this mode given as

$$i_A = i_A(t_5) - \frac{V_{dc}}{2L_{Ik}}(t - t_5)$$

(9)

Fig. 13. Mode 6: Circuit diagram and equivalent circuit.

Fig. 14. Mode 7: Circuit diagram and equivalent circuit.

$i_A$  falls to zero and changes its direction at  $t_C$ . To ensure ZVS ON,  $S_{A2}^\prime$  is turned ON when the antiparallel diode is conducting. The duration  $(t_C-t_5)$  is given as

$$t_C - t_5 = \frac{2L_{lk}i_A(t_5)}{V_{dc}}. (10)$$

In secondary, linear current commutation between diode pairs  $(D_{1,4}), (D_{2,3})$  takes place. Current through  $D_1$  and  $D_2$  are shown in Fig. 6.

#### F. Mode 6 ( $t_C < t < t_6$ , Fig. 13)

As  $S_{A2}'$  is turned ON in between  $t_5$  and  $t_C$ ,  $i_A$  can grow in the opposite direction after  $t_C$ . Current commutation continues between the diode pairs  $(D_{1,4})$ ,  $(D_{2,3})$ .  $i_A$  changes linearly as expressed in (9). The mode ends at  $t_6$  when  $i_A = -nI_x$ .

# G. Mode 7 ( $t > t_6$ , Fig. 14)

After  $t_6$ ,  $D_1$  and  $D_4$  are reverse biased and stop conducting.  $D_2$  and  $D_3$  conduct  $I_x$ . In the primary  $S_{A2}'$  and  $S_{A2}$  are conducting  $i_A$ . The equivalent circuit is shown in Fig. 14. The converter is in next active state where the active power is transferred from dc source to load such as in Mode 1.

The above discussion shows the operation of the 3 L-NPC leg over one-half of a switching cycle. In the other half, similar switching sequences are followed with other symmetrical switches and ZCS turn-ON of  $S_{A1}$  and ZVS turn-ON of  $S_{A1}'$  are

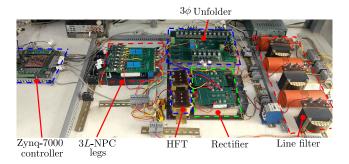

Fig. 15. Hardware prototype.

ensured similar to  $S_{A2}$  and  $S_{A2}^{\prime}$ , respectively, as discussed in Modes 3 and 5.

#### H. Estimation of Upper Limit of Dead Time to Ensure ZVS

As discussed above, the pole current  $i_A$  changes its direction during the switching transitions of  $S'_{A1} - S'_{A2}$ . To ensure zero voltage turn-ON of  $S'_{A1} - S'_{A2}$ , the switches must be gated ON when the antiparallel diode is in conduction before the direction of  $i_A$  is changed. Hence, the dead time between  $S'_{A1} - S'_{A2}$ cannot be arbitrary and has upper and lower bounds. To allow the complete charge-discharge of the device capacitances, the dead time should be greater than the interval  $(t_5 - t_4)$  as given in (8). The upper bound of dead time is  $(t_C - t_4)$ , where  $t_C$  is the zero cross over point of  $i_A$ .  $(t_C - t_5)$  is given in (10). As seen in (8) and (10), the intervals are dependent on  $I_x$  which is the magnitude of  $i_x$  over a switching cycle. In Fig. 3,  $i_x$  over a line cycle is shown for UPF operation. The bounds on the dead time are most strict at the minimum value of  $i_x$  which is  $0.5I_{pk}$ . Hence, replacing  $I_x$  with  $0.5I_{pk}$ , following limits on dead time DT are obtained as

$$DT \ge (t_5 - t_4)_{\text{max}} = \frac{1}{\omega_r} \sin^{-1} \left( \frac{V_{\text{dc}}}{n\omega_r L_{lk} I_{pk}} \right)$$

$$DT \le (t_5 - t_4)_{\text{max}} + (t_C - t_5)_{\text{min}}$$

$$= \frac{1}{\omega_r} \left[ \sin^{-1} \left( \frac{V_{\text{dc}}}{n\omega_r L_{lk} I_{pk}} \right) + \sqrt{\left( \frac{n\omega_r L_{lk} I_{pk}}{V_{\text{dc}}} \right)^2 - 1} \right]$$

which ensures ZVS turn-ON of  $S'_{A1} - S'_{A2}$  over the entire line cycle. For a given input  $V_{\rm dc}$  and the circuit parasitics  $(C_s, L_{lk})$ , the bounds are dependent on  $I_{pk}$ , i.e., output power P. For a given operation range of the converter if (11) is ensured for the minimum value of  $I_{pk}$ , ZVS of  $S'_{A1} - S'_{A2}$  can be ensured for the complete range of operation.

#### IV. EXPERIMENTAL VERIFICATION

#### A. Operating Condition

To verify the operation of the proposed inverter, a 2-kW laboratory scale hardware prototype is built and tested. Fig. 15 shows the test setup. The operating condition of the converter is

TABLE III

OPERATING CONDITION

| Output power (P)                               | 2.05kW |  |  |

|------------------------------------------------|--------|--|--|

| DC input $(V_{dc})$                            | 460V   |  |  |

| Peak phase voltage $(V_{pk})$                  | 156V   |  |  |

| HFT turns ratio (n)                            | 4/3    |  |  |

| Switching frequency $(f_s = \frac{1}{T_s})$    | 20kHz  |  |  |

| Line frequency $(f_o = \frac{\omega_o}{2\pi})$ | 50Hz   |  |  |

presented in Table III. The 3 L-NPC legs are implemented with 1200 V, 75 A SEMIKRON IGBT modules, SKM75GB123D. The neutral clamp diodes are implemented with 1200 V, 75 A IXYS diode modules, MEE 75-12 DA. These diode modules are also used to build the secondary rectifiers. INFINEON IKW40N120H3 discrete IGBTs (1200 V, 40 A) are used in the secondary unfolder. All the IGBTs are driven with optically isolated gate drivers, ACPL 339 J with gate voltage levels  $\pm 15$ V. A 600-ns dead time is provided between to complementary switched devices in the 3 L-NPC legs. A 800-ns overlap time is given between to successive gating signals of an unfolder leg. The HFTs are implemented with EPCOS ferrite E cores (E80/38/20). The primary and secondary turns of a HFT are 51 and 68, respectively. The transformers have leakage inductances (seen from primary) in the order of 5–6  $\mu$ H. To ensure ZVS turn ON of the 3 L-NPC leg switches, additional 36- $\mu$ H inductance is connected in series with each primary winding. A 2.5-mH inductors  $(L_f)$  are used as line filters to filter out the HF component from the line currents.

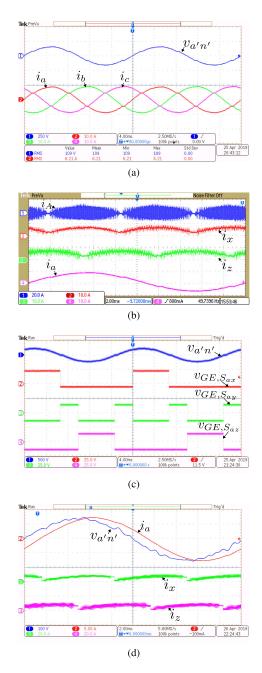

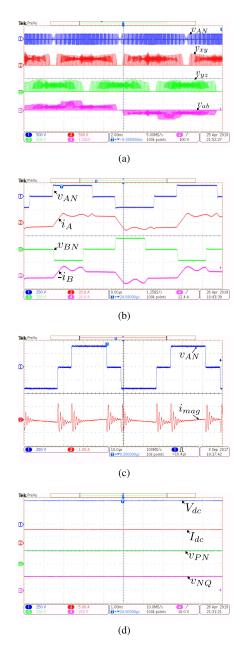

#### B. Experimental Verification of Modulation Strategy

The balanced three-phase output of the converter is shown in Fig. 16(a). The converter is connected to a balanced three-phase voltage source supplying 2.05-kW power (P) at UPF. Peak of the output phase voltage  $V_{pk}$  is 156 V. Balanced three-phase line currents with peak  $I_{pk}=\frac{2P}{3V_{pk}}=8.8\,\mathrm{A}$  are shown in Fig. 16(a).

Fig. 16(b) shows the transformer primary current  $i_A$ , the rectifier output currents  $i_x$ ,  $i_z$  and the line current  $i_a$ . The transformer primary current  $i_A$  is HF square wave with sinusoidally varying magnitude.  $i_A$  has a peak magnitude of  $nI_{pk}=11.7$  A. The experimentally obtained rectifier output currents  $i_x$  and  $i_z$  have similar shapes as shown in Fig. 3 and have peak magnitude of  $I_{pk}=8.8$  A.

The unfolder switching strategy is shown in Fig. 16(c). Based on the switching states given in Table I, gating signals of the unfolder are obtained. It is seen that the two quadrant switches  $(S_{ax,az})$  are line frequency (50 Hz) switched whereas the four-quadrant switch  $(S_{ay})$  are switched twice of the line frequency (at 100 Hz). Hence, the unfolder obtained negligible switching loss.

The proposed topology can support stand-alone load up to  $30^{\circ}$  leading and lagging power factor. Fig. 16(d) shows the converter operation supporting a 0.9-PF inductive load. The line current  $i_a$  lags  $v_{a'n'}$  by  $25.2^{\circ}$ . The result also shows rectifier output currents  $i_x$  and  $i_z$ . Differences in shape of  $i_x$  and  $i_z$  at UPF [see Fig. 16(b)] and at lagging PF operation are observable. For

Fig. 16. (a) UPF operation [CH1]  $v_{a'n'}$  (250 V/div), [CH2]–[CH4]: Line currents (10 A/div). (b) Current waveforms [CH1]:  $i_A$  (20 A/div), [CH2]–[CH4]:  $i_x$ ,  $i_z$ ,  $i_a$  (10 A/div). (c) Unfolder switching [CH1]  $v_{a'n'}$  (500 V/div), [CH2]–[CH4]: Gate-emitter voltages of  $S_{ax}$ ,  $S_{ay}$ ,  $S_{az}$  (25 V/div). (d) Non-UPF operation (PF: 0.9 lagging) [CH1]:  $v_{a'n'}$  (100 V/div), [CH2]:  $i_a$  (5 A/div), [CH3]–[CH4]:  $i_x$  and  $i_z$  (20 A/div).

both the cases,  $i_x$  and  $i_z$  are always positive over the line cycle. Similarly other nonunity power factor operation of the converter can be verified.

The pulsewidth modulated HF ac  $(v_{AN})$  applied across transformer primary is shown in Fig. 17(a).  $v_{AN}$  has voltage levels of  $\pm 230$  V and 0 V. Fig. 17(a) also shows the rectifier output voltages  $v_{xy}$  and  $v_{yz}$  with voltage levels  $0.5nV_{\rm dc}=307$  V and 0. As discussed in Section II, the intermediate dc link xy and

Fig. 17. (a) Pole voltages: [CH1]–[CH3]:  $v_{AN}$ ,  $v_{xy}$ ,  $v_{yz}$  (500 V/div), [CH4]  $v_{ab}$  (1 kV/div). (b) Transformer waveforms over switching cycle [CH1]  $v_{AN}$  (250 V/div), [CH2]:  $i_A$  (20 A/div), [CH3]:  $v_{BN}$  (250 V/div), [CH4]:  $-i_B$  (20 A/div). (c) HFT magnetizing current, [CH1]:  $v_{AN}$  (250 V/div), [CH2]:  $i_{mag}$  (1 A/div). (d) DC inputs [CH1]:  $V_{dc}$  (250 V/div), [CH2]:  $I_{dc}$  (5 A/div), [CH3]:  $v_{PN}$  (250 V/div), [CH4]:  $v_{NQ}$  (250 V/div).

yz are pulsating as no filter capacitor is employed. The unfolder pole voltage  $v_{ab}$  is also shown in Fig. 17(a).

The transformer primary voltages and primary currents over a switching cycle are shown in Fig. 17(b). Experimentally measured applied voltages  $v_{AN}$  and  $v_{BN}$  are matched with the waveforms shown in Fig. 5. The polarity of applied voltages are opposite. This verifies the modulation strategy of the 3 L-NPC legs to ensure reduced neutral current as described in Section II.

Fig. 17(c) shows the experimentally measured magnetizing current waveform of the HFT and the transformer primary voltage over a switching cycle. As the transformer primary

voltages have zero average over the switching cycle, hence, flux is balanced over the switching cycle. The HF oscillation observed in the magnetizing current is due to parasitic ringing of the transformer during the switching transitions.

Fig. 17(d) shows the input voltages and input current of the converter. The applied input voltage is 460 V and input current is 5 A. The input dc-link voltages are  $v_{PN}=v_{NQ}=230$  V. As seen in the figure,  $v_{PN}$  and  $v_{NQ}$  have negligible ripple, hence, no neutral voltage unbalance is observed.

# C. Experimental Verification of Soft-Switching Transitions of the 3 L-NPC Leg A

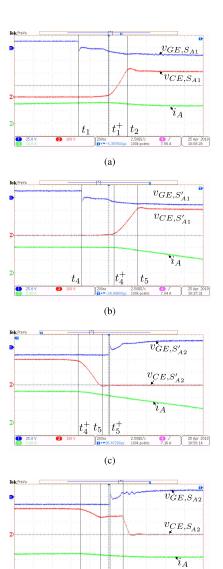

In this section, the experimental results are presented to verify following switching transitions of the 3 L-NPC leg A- turn-OFF transitions of  $S_{A1}$ ,  $S'_{A1}$  and the turn ON of  $S'_{A2}$ ,  $S_{A2}$ .

Fig. 18(a) shows the turn OFF transition of  $S_{A1}$ . Before  $t_1$ ,  $S_{A1}$  was ON and conducting  $i_A$ . At  $t_1$ , the gating pulse of  $S_{A1}$  is removed. After some time at  $t_1^+$ , when the gate emitter voltage of  $S_{A1}$ ,  $v_{GE,S_{A1}}$  becomes negative, the voltage across the device,  $v_{CE,S_{A1}}$  starts to rise slowly and at  $t_2$ ,  $S_{A1}$  blocks  $0.5V_{\rm dc}$ . The slow rise of the voltage across the device is due to device capacitance ( $C_s$ ) which helps to reduce the turn-OFF loss of  $S_{A1}$ . The result verifies the switching process described in Mode 2 of Section III.

Fig. 18(b) presents the turn-OFF transition of  $S'_{A1}$ . At  $t_4$ , the gating pulse is removed. At  $t_4^+$ , when the gate emitter voltage of  $S'_{A1}$ ,  $v_{GE,S'_{A1}}$  is negative, the voltage across the device,  $v_{CE,S'_{A1}}$  starts to rise slowly and at  $t_5$ ,  $v_{GE,S'_{A1}}$  rises to  $0.5V_{\rm dc}$ . The slow change in  $v_{CE,S'_{A1}}$  is due to device capacitance which helps to reduce turn-OFF loss of  $S'_{A1}$ . After  $t_5$ ,  $i_A$  falls linearly. The result verifies the switching process described in Mode 4 of Section III.

The experimental result shown in Fig. 18(c) verifies the ZVS turn-ON of  $S_{A2}'$  described in Modes 4 and 5 of Section III.  $S_{A2}'$  was OFF and was blocking 0.5  $V_{\rm dc}$ . At  $t_4^+$ ,  $i_A$  starts to discharge the capacitance across  $S_{A2}'$ . The voltage across the device,  $v_{CE,S_{A2}'}$  falls to zero at  $t_5$  and the antiparallel diode of  $S_{A2}'$  starts conducting  $i_A$ . At  $t_5^+$ , before  $i_A$  changes its direction, the gating pulse of  $S_{A2}'$  is applied to ensure ZVS turn-ON.

The turn-ON process of  $S_{A2}$  is shown in Fig. 18(d). At  $t_1^+$ , the voltage across  $S_{A2}, v_{CE,S_{A2}}$  starts to fall from  $0.5 \, \mathrm{V_{dc}}$ . At  $t_2, v_{CE,S_{A2}} = 0.5 \, \mathrm{KV_{dc}} = 140 \, \mathrm{V}$  and  $S_{A2}$  continues to block  $0.5 \, \mathrm{KV_{dc}}$ . At  $t_3^-$ , the gating pulse of  $S_{A2}$  is applied. When the gate emitter voltage,  $v_{GE,S_{A2}}$  rises above the device threshold voltage at  $t_3$ , the device channel starts conducting. The device capacitance discharges through the channel. As the direction of  $i_A$  remains same,  $S_{A2}$  does not conduct even after turn-ON. Hence, the turn-ON of  $S_{A2}$  is zero current transition (ZCS). The loss due to parasitic discharge into the channel is small as the blocking voltage  $(0.5 \, \mathrm{KV_{dc}})$  and the capacitance both are small. The result verifies the process described in Modes 2 and 3 of Section III.

### D. Power Loss and Efficiency

The converter power loss is analytically estimated assuming ripple free line currents. In the analysis, only conduction loss

Fig. 18. Switching transition waveforms (a) Turn-OFF of  $S_{A1}$ . (b) Turn-OFF of  $S_{A1}'$ . (c) Turn-ON of  $S_{A2}'$ . (d) Turn-ON of  $S_{A2}$ .

(d)

is considered as the proposed topology is soft-switched. The experimentally measured power loss verifies the analysis.

1) Analytical Loss Expressions: The conduction loss in switch  $S_{A1}$  is given as

$$P_{C_{S_{A1}}} = 0.25MV_{CE}(nI_{pk}) + 0.23MR_{CE}(nI_{pk})^2$$

(12)

where  $V_{CE}$  and  $R_{CE}$  are constant voltage drop and ON-state resistance, respectively, of the IGBT module.  $I_{pk}$  is the peak of the line current. The conduction loss in switch  $S'_{A1}$  is given as

$$P_{C_{S'_{A1}}} = 0.41V_{CE}(nI_{pk}) + 0.35(nI_{pk})^2 R_{CE}.$$

(13)

The conduction loss in diode  $D_A$  is given as

$$P_{C_{D_A}} = (0.41 - 0.25M)V_{CE}(nI_{pk}) + (0.35 - 0.23M)(nI_{pk})^2 R_{CE}$$

(14)

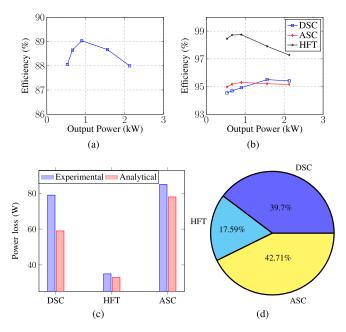

Fig. 19. (a) Variation of efficiency with load. (b) Stage wise efficiency of the converter. (c) Loss distribution estimated analytically and obtained experimentally at 1.54 kW. (d) Share of loss at 1.54 kW output power.

where  $V_D$  and  $R_D$  are constant voltage drop and ON-state resistance, respectively, of the diode module. As the DSC is soft-switched, switching loss is negligible.

The conduction loss in an ASC diode of  $D_1 - D_8$  is given as

$$P_{C_{D_1}} = 0.41 V_D I_{pk} + 0.36 R_D I_{pk}^2.16$$

The conduction loss in an ASC four quadrant switch of  $S_{a,b,c(y)}$  is given as

$$P_{C_{S_{au}}} = 0.04V_{CE}I_{pk} + 0.014R_{CE}I_{pk}^2. (17)$$

The conduction loss in an antiparallel diode of the four quadrant switches  $S_{a,b,c(y)}$  is given as

$$P_{C_{D_{Say}}} = 0.04V_D I_{pk} + 0.014R_D I_{pk}^2. (18)$$

As ASC active switches are low frequency switched, the switching loss is negligible.

The copper loss of an HFT is given as  $I_{A,\mathrm{rms}}^2(R_p + \frac{R_s}{n^2})$ , where  $I_{A,\mathrm{rms}} = 0.84 n I_{pk}$  is the rms current of the primary winding.  $R_p$  and  $R_s$  are resistance of the primary and secondary windings. At the switching frequency, the HFT core loss is negligible.

2) Experimental Measurement of Converter Power Loss: The converter was operated with fixed input dc 420 V, delivering a range of output power, 0.53–2.13 kW. The power loss of various stages of the converter was measured. The variation of efficiency with load power is shown in Fig. 19(a). The hardware prototype has maximum efficiency 89% at 0.9-kW output power. The efficiency of the three stages (DSC, ASC, and HFT) of the converter are shown in Fig. 19(b). The DSC and ASC stages have above 95% efficiency individually almost throughout the load range 19(b). The efficiency of the DSC improves with higher power output as expected. Because at high power, the DSC is soft-switched throughout the line cycle. The low frequency

switched ASC has almost constant efficiency profile with the variation of load. The HFT loss increases with increased load. The experimentally obtained and analytical estimated losses at the different stages of the converter at 1.56-kW output power are shown in Fig. 19(c). The analytically estimated power losses are closely matched with the experimentally obtained values. A pie chart showing the share of loss in different stages at 1.56 kW output power is shown in Fig. 19(d). The experimental prototype of the proposed topology is also not optimally designed for 2–3 kW power level and hence has the relatively low peak efficiency of 89%. With an optimally designed converter at 2-kW output powers, an analytically estimated overall efficiency of 95.5% can be achieved. The method of analytical estimation is verified with the existing hardware [see Fig. 19(c)].

#### V. COMPARISON WITH OTHER TOPOLOGIES

The proposed topology is compared with two single-stage unidirectional three-phase HFL inverter topologies given in [12] and [13]. Like the proposed topology, these selected topologies can support VAr up to  $\pm 0.866$  power factor. To perform the comparison fairly, all the topologies under consideration are designed for same operating conditions with given input and output voltages and output power. The switching frequency and modulation index (0.85) are considered same for all the topologies. All the topologies are modulated at 85% of its maximum possible modulation index. For generalization, the parameters of the comparison are evaluated in terms of output power (P), input dc voltage  $(V_{\rm dc})$  or peak output voltage  $(V_{pk})$ , and switching frequency  $(f_s)$ .

Table IV summarizes the topology comparison. It presents the number of active and passive semiconductors employed, their blocking voltages  $(V_b)$ , rms  $(I_{\rm rms})$  currents. S.F is the scaling factor. Total number of semiconductors employed in the proposed topology is same as [13]. Though the number of active devices used in the proposed topology is higher compared to [12], but majority of these switches are line frequency switched. The blocking voltage of the DSC devices of the proposed topology are half of [12], [13] and have relatively higher rms currents. The ASC devices have similar rms currents. The DSC of the proposed topology is soft-switched whereas the ASC is low frequency switched. In [12] and [13], DSCs and ASCs are hard-switched.

The proposed solution has two HFTs, similar to the topology in [13] with comparable area product, and [12] has three HFTs.

Table V summarizes the power loss comparison. To perform a thorough comparison of the converter power losses, the conduction losses of the DSC switches are further expressed in terms of  $\frac{V_{CE}P}{V_{\rm dc}}$  and  $\frac{R_{CE}P^2}{V_{\rm dc}^2}$ . For diodes  $R_{CE}$ ,  $V_{CE}$  are replaced with  $R_D$ ,  $V_D$ , respectively. In the case of ASC switches and diodes  $V_{\rm dc}$  of the scaling factors are replaced with  $V_{pk}$ . The switching losses of the active switches are also expressed in terms of  $\frac{f_s PE_R}{P_R}$  where  $E_R = E_{\rm ON_R} + E_{\rm OFF_R}$  and  $P_R = V_{CC}I_C$ .  $E_{\rm ON_R}$  and  $E_{\rm OFF_R}$  are respectively, the turn ON and OFF energy losses of the devices given at rated conditions,  $V_{CC}$  and  $I_C$ .

TABLE IV

TOPOLOGY COMPARISON: DEVICES AND HFTs

|     |                 | S.F                       | [12]                            | [13]                        | Proposed<br>Topology      |

|-----|-----------------|---------------------------|---------------------------------|-----------------------------|---------------------------|

|     | Switch count    | _                         | 6                               | 8                           | 8                         |

|     | Diode<br>count  | _                         | _                               | _                           | 4                         |

| DSC | $V_{b,sw}$      | $V_{dc}$                  | 1                               | 1                           | 0.5                       |

|     | $I_{RMS,sw}$    | $\frac{P}{V_{dc}}$        | 0.58                            | 0.49/0.43                   | 1.0/ 1.4                  |

|     | Switching       | _                         | Hard-<br>switched               | Hard-<br>switched           | Soft-<br>switched         |

|     | switch<br>count | _                         | 6                               | 12                          | 12                        |

|     | Diode<br>count  | _                         | 6                               | 14                          | 8                         |

| ASC | $V_{b,sw}$      | $V_{pk}$                  | 2.04                            | 1.2                         | 3.5/1.76                  |

|     | $I_{RMS,sw}$    | $\frac{P}{V_{pk}}$        | 0.33 /<br>0.302                 | 0.33/ 0.414                 | 0.323/<br>0.396           |

|     | Switching       | _                         | High-freq.<br>hard-<br>switched | High-freq.<br>hard-switched | Line<br>freq.<br>switched |

|     | HFT count       | _                         | 3                               | 2                           | 2                         |

| HFT | $I_{RMS,pri}$   | $\frac{P}{V_{dc}}$        | 0.87                            | 0.685                       | 1.976                     |

|     | $I_{RMS,sec}$   | $\frac{P}{V_{pk}}$        | 0.43                            | 0.58                        | 0.56                      |

|     | Area<br>product | $\frac{P}{f_s J B_m K_w}$ | 0.2                             | 0.3                         | 0.42                      |

TABLE V

TOPOLOGY COMPARISON-POWER LOSS

| Topology |       |                                            | DSC    |       |                              | ASC    |       |

|----------|-------|--------------------------------------------|--------|-------|------------------------------|--------|-------|

|          |       | S.F.                                       | Switch | Diode | S.F.                         | Switch | Diode |

| Proposed | $P_C$ | $\frac{V_{CE}P}{V_{dc}}$                   | 5.86   | 1.86  | $\frac{V_{CE}P}{V_{pk}}$     | 1.26   | 2.347 |

|          |       | $\frac{R_{CE}P^2}{V_{dc}^2}$               | 12.1   | 3.42  | $\frac{R_{CE}P^2}{V_{pk}^2}$ | 0.664  | 1.317 |

|          | $P_S$ | $\frac{PE_Rf_s}{P_R}$                      | 0      |       | $\frac{PE_Rf_s}{P_R}$        | 0      |       |

|          | $P_C$ | $\frac{\frac{V_{CE}P}{V_{dc}}}{R_{CE}P^2}$ | 2.25   | 0.25  | $\frac{V_{CE}P}{V_{pk}}$     | 1.21   | 1.26  |

| [12]     |       | $V_{dc}^2$                                 | 1.97   | 0.3   | $\frac{R_{CE}P^2}{V_{pk}^2}$ | 0.65   | 0.853 |

|          | $P_S$ | $\frac{PE_Rf_s}{P_R}$                      | 7.34   |       | $\frac{PE_Rf_s}{P_R}$        | 0.696  |       |

| [13]     | $P_C$ | $\frac{V_{CE}P}{V_{dc}}$                   | 2.35   | 0.354 | $\frac{V_{CEP}}{V_{pk}}$     | 2.45   | 2.434 |

|          |       | $\frac{R_{CE}P^2}{V_{dc}^2}$               | 1.654  | 0.17  | $\frac{R_{CE}P^2}{V_{pk}^2}$ | 1.32   | 1.4   |

|          | $P_S$ | $\frac{PE_Rf_s}{P_R}$                      | 5.4    |       | $\frac{PE_Rf_s}{P_R}$        | 1.26   |       |

The blocking voltage of DSC devices of the proposed topology, is half and the rms current is more than twice of [12] and [13].  $V_{CE}$  and  $R_{CE}$  are the function of device blocking voltage and rms currents.  $V_{CE}$  reduces with blocking voltage of the devices and  $R_{CE}$  comes down with increased rms current. Hence, the DSC devices of the proposed topology have lower  $V_{CE}$  and  $R_{CE}$  compared to [12] and [13].

Though the conduction loss factors of the DSC devices and diodes are higher, as these devices and diodes have lower  $V_{CE}$  and  $R_{CE}$  compared to [13], the DSC has comparable conduction loss. The conduction loss of the ASC devices are half of [13] and comparable with [12]. The ASC diodes have comparable conduction losses with [13]. ASC diode of [12] has lower conduction loss compared to the proposed solution.

The DSC of the proposed topology is soft-switched throughout the line cycle. The ASC is line frequency switched incurring negligible switching loss. As the topologies in [12] and [13] are HF hard-switched, it incurs significant switching loss.

#### VI. CONCLUSION

A novel three-level three-phase HFL single stage dc-ac converter is presented in this article for the applications such as grid integration of photovoltaics. The proposed topology employs three-level NPC legs on the dc side of the converter. Hence, the low voltage rating devices with lower ON-state drop and lower  $E_{\rm ON}$  and  $E_{\rm OFF}$  can be used to implement the dc side bridge compared to a two-level-based solution. Additionally, the inner switches of the three-level NPC legs are zero voltage switched (ZVS). Whereas the turn-ON of the outer switches are zero current transitions (ZCS). Proposed modulation strategy of the three-level NPC legs ensures reduced neutral current. The pulsewidth modulation is implemented on the dc side bridge. The interstage dc link after the secondary rectifiers is pulsating as no filter capacitor is employed. The unfolder active switches are switched either at line frequency or twice of the line frequency, hence incurring negligible switching loss. The converter can support stand-alone load up to 30° leading or lagging power factor. The detailed modulation strategy of the converter and switching process of the three-level NPC legs are discussed in the article. Conditions ensuring ZVS operation over a complete line cycle are derived. A 2-kW hardware prototype is built and tested. Experimental results are presented to verify the converter operation at UPF and 0.9 lagging PF operation. The proposed topology is compared with two other unidirectional single stage solutions. Compared to the other topologies, the proposed topology achieves complete unfolding of the ASC and soft-switching of the DSC. The proposed topology with HF galvanic isolation provides a compact, high power density, low-cost converter solution.

#### REFERENCES

- S. Essakiappan, H. S. Krishnamoorthy, P. Enjeti, R. S. Balog, and S. Ahmed, "Multilevel medium-frequency link inverter for utility scale photovoltaic integration," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3674–3684, Jul. 2015.

- [2] K. V. Iyer, R. Baranwal, and N. Mohan, "A high-frequency ac-link single-stage asymmetrical multilevel converter for grid integration of renewable energy systems," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5087–5108, Jul. 2017.

- [3] K. V. Iyer and N. Mohan, "Modulation and commutation of a single stage isolated asymmetrical multilevel converter for the integration of renewables and battery energy storage system in ships," *IEEE Trans. Transp. Electrific.*, vol. 2, no. 4, pp. 580–596, Dec. 2016.

- [4] U. R. Prasanna and A. K. Rathore, "A novel single-reference six-pulse-modulation (SRSPM) technique-based interleaved high-frequency three-phase inverter for fuel cell vehicles," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5547–5556, Dec. 2013.

- [5] S. Norrga, S. Meier, and S. Ostlund, "A three-phase soft-switched isolated ac/dc converter without auxiliary circuit," *IEEE Trans. Ind. Appl.*, vol. 44, no. 3, pp. 836–844, May/Jun. 2008.

- [6] K. Basu and N. Mohan, "A high-frequency link single-stage PWM inverter with common-mode voltage suppression and source-based commutation of leakage energy," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 3907– 3918, Aug. 2014.

- [7] M. Matsui, M. Nagai, M. Mochizuki, and A. Nabae, "High-frequency link dc/ac converter with suppressed voltage clamp circuits-naturally commutated phase angle control with self turn-off devices," *IEEE Trans. Ind. Appl.*, vol. 32, no. 2, pp. 293–300, Mar./Apr. 1996.

- [8] R. Huang and S. K. Mazumder, "A soft-switching scheme for an isolated dc/dc converter with pulsating dc output for a three-phase high-frequencylink PWM converter," *IEEE Trans. Power Electron.*, vol. 24, no. 10, pp. 2276–2288, Oct. 2009.

- [9] D. De and V. Ramanarayanan, "Analysis, design, modeling, and implementation of an active clamp HF link converter," *IEEE Trans. Circuits Syst. I: Regular Papers*, vol. 58, no. 6, pp. 1446–1455, Jun. 2011.

- [10] S. K. Mazumder and R. Huang, "A soft switching scheme for multiphase dc-pulsating dc converter for three-phase high-frequency-link pulsewidth modulation (PWM) inverter," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1761–1774, Jul. 2010.

- [11] A. Rahnamaee and S. K. Mazumder, "A soft-switched hybrid-modulation scheme for a capacitor-less three-phase pulsating-dc-link inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 3893–3906, Aug. 2014.

- [12] S. K. Mazumder, "Hybrid modulation scheme for a high-frequency aclink inverter," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 861–870, Jan. 2016.

- [13] A. d. E. Dutra, M. A. Vitorino, R. P. R. de Sousa, M. B. Corrêa, and G. G. dos Santos, "High-frequency pulsating dc-link three-phase multilevel NPC inverter without electrolytic capacitor," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2018, pp. 1348–1355.

- [14] A. Pal and K. Basu, "A unidirectional single-stage three-phase soft-switched isolated dc-ac converter," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1142–1158, Feb. 2019.

- [15] A. Pal and K. Basu, "A soft-switched high frequency link single-stage three-phase inverter for grid integration of utility scale renewables," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 8513–8527, Sep. 2019.

- [16] IEEE Recommended Practice for Utility Interface of Photovoltaic (PV) Systems, IEEE Standard 929-2000, 2000.

- [17] R. Teichmann and S. Bernet, "A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications," *IEEE Trans. Ind. Appl.*, vol. 41, no. 3, pp. 855–865, May/Jun. 2005.

- [18] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparative evaluation of advanced three-phase three-level inverter/converter topologies against two-level systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5515–5527, Dec. 2013.

- [19] J. R. Pinheiro and I. Barbi, "The three-level ZVS-PWM dc-to-dc converter," *IEEE Trans. Power Electron.*, vol. 8, no. 4, pp. 486–492, Oct. 1993.

- [20] E.-S. Kim, Y.-B. Byun, T.-G. Koo, K.-Y. Joe, and Y.-H. Kim, "An improved three level ZVZCS dc/dc converter using a tapped inductor and a snubber capacitor," in *Proc. Power Convers. Conf.-Osaka*, 2002, vol. 1, pp. 115– 121.

- [21] D. V. Ghodke, K. Chatterjee, and B. Fernandes, "Modified soft-switched three-phase three-level dc-dc converter for high-power applications having extended duty cycle range," *IEEE Trans. Ind. Electron.*, vol. 59, no. 9, pp. 3362–3372, Sep. 2012.

- [22] F. Liu, Y. Chen, G. Hu, and X. Ruan, "Modified three-phase three-level dc/dc converter with zero-voltage-switching characteristic-adopting asymmetrical duty cycle control," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6307–6318, Dec. 2014.

- [23] M. Narimani and G. Moschopoulos, "An investigation on the novel use of high-power three-level converter topologies to improve light-load efficiency in low power dc/dc full-bridge converters," *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5690–5692, Oct. 2014.

- [24] J. Khodabakhsh, R. Rasoulinezhad, and G. Moschopoulos, "Using multilevel ZVZCS converters to improve light-load efficiency in low power applications," *IEEE Trans. Power Electron.*, vol. 34, no. 12, pp. 11536–11540, Dec. 2019.

- [25] A. Pal and K. Basu, "A unidirectional soft-switched isolated three level inverter for grid integration of renewable energy sources," in *Proc. IEEE Int. Conf. Signal Process., Inform., Commun. Energy Syst.*, 2017, pp. 1–6.

Anirban Pal (Student Member, IEEE) received the B.E. degree from the Indian Institute of Engineering Science and Technology, Shibpur, Howrah, India, in 2010, and the M.E. degree from the Indian Institute of Science, Bangalore, India, in 2015, both in electrical engineering. He is currently working toward the Ph.D. degree with the Electrical Engineering Department, Indian Institute of Science.

From 2010 to 2013, he was an Assistant Manager with the National Thermal Power Corporation Limited, New Delhi, India. His research interests include

HFL inverters, dual active bridge converters, resonant converters, soft-switching techniques, design of high-frequency magnetics.

Kaushik Basu (Senior Member, IEEE) received the B.E. degree from the Bengal Engineering and Science University, Shibpur, Howrah, India, in 2003, the M.S. degree in electrical engineering from the Indian Institute of Science, Bangalore, India, in 2005, and the Ph.D. degree in electrical engineering from the University of Minnesota, Minneapolis, MN, USA, in 2012

He was a Design Engineer with Cold Watt India, Bangalore, India, in 2006, and an Electronics and Control Engineer with Dynapower Corporation,

South Burlington, VT, USA, from 2013 to 2015. Currently, he is an Assistant Professor with the Department of Electrical Engineering, Indian Institute of Science. He has authored and coauthored several technical papers published in peer-reviewed journals and conferences. His research interests include various aspects of the general area of power electronics.

Dr. Basu is the Founding Chair of both IEEE PELS and IES Bangalore Chapter.